New performance-enhancing features in modern processors can mean it is harder, not easier, to establish the worst-case execution time (WCET) of an application. Why is this happening?

Real-time systems and WCET

A real-time system is generally considered to be one where the correctness of the system depends not only on the result produced by that system, but also on the time at which that result is produced. In lots of systems, this translates directly into the concept of deadlines: a time by which a particular calculation must be complete or a result must be provided. Failure to meet deadlines causes problems, which depending on the system may range from inconvenient to catastrophic.

New hardware features and WCET

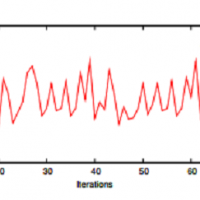

As systems have become larger and more complicated, it's become increasingly difficult to establish a value for the worst-case execution time. In part, this is because the software itself is larger and so there are a larger number of possible paths that the execution can follow. However, a significant difficulty is posed by new performance-enhancing features that are included in modern processors. Features like pipelined architectures, instruction and data caches and multicore processors make it much more difficult to establish the WCET and therefore, more difficult to guarantee that a system will meet its deadlines.

At first glance this may appear counter-intuitive: how can a feature that's supposed to improve performance make it more difficult to guarantee that deadlines are met? The key here is that the new hardware features are concerned with improving average case performance. Frequently the average case is improved dramatically, but at the expense of making it difficult to establish what happens in the worst-case.

This is because the state of the hardware, as well as the execution behaviour of the software, now has an effect on the execution time - for example, if a function requires access to some data, the execution time of that function will be less if that data is stored in a cache than it would be if the data must be retrieved from RAM. Often, methods to work around this behaviour lead to increasingly pessimistic results.

RapiTime and WCET

Developers of real-time systems spend lots of time and effort ensuring that their systems are schedulable, i.e. that they will always meet their deadlines. At Rapita, we help with this by providing RapiTime - a software toolset that allows the WCET for an application to be established. If you can prove that the system will meet all its deadlines even if everything runs for its WCET, you can be confident that the system won't fail because of a timing problem.

In future posts, we'll consider some of the technologies that make real-time analysis difficult in more detail, and examine some of the techniques that can be used with RapiTime to help to determine the WCET in systems that use them.

RVS 3.24 accelerates multicore software verification

RVS 3.24 accelerates multicore software verification

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Retro gaming with the Sim68020

Retro gaming with the Sim68020

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

Test what you fly - Real code, Real Conditions Webinar

Test what you fly - Real code, Real Conditions Webinar

Avionics Certification Q&A: CERT TALK

Avionics Certification Q&A: CERT TALK

XPONENTIAL 2026

XPONENTIAL 2026

DO-178C Multicore In-person Training (Heathrow)

DO-178C Multicore In-person Training (Heathrow)