Analysis of the timing behavior of avionics software helps avoid errors such as timing overruns and is needed to support DO-178C certification.

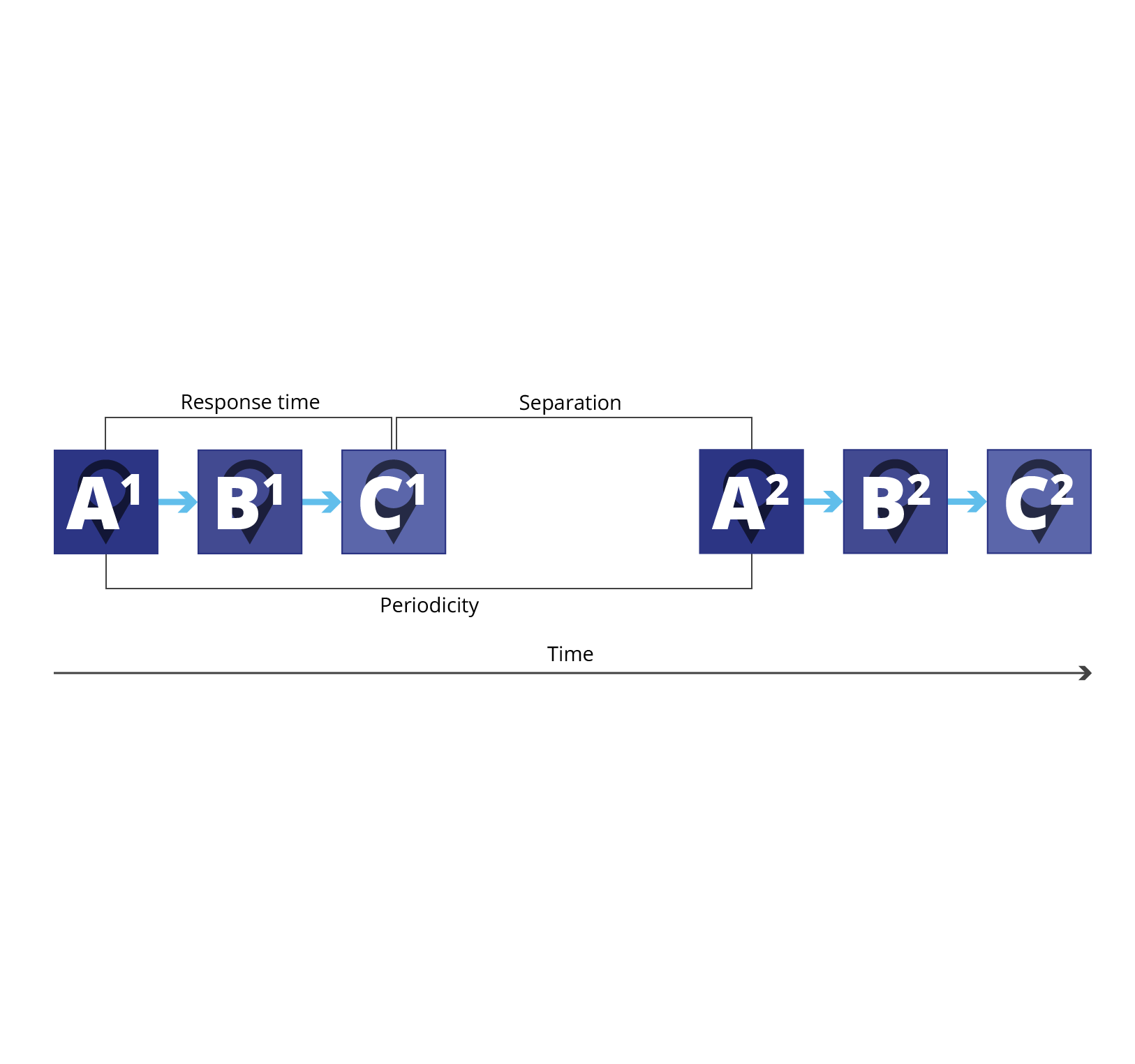

While many timing requirements relate to the worst-case execution time of software, some may relate to other metrics such as response time, periodicity of execution, or separation between different instances of a sequence running.

Execution time vs. response time

The execution time of a piece of software is the time taken for a task to finish, ignoring time spent executing other functions or interrupts.

The response time of a piece of software is the total time taken for a task to finish, including time spent executing code in other functions or interrupts.

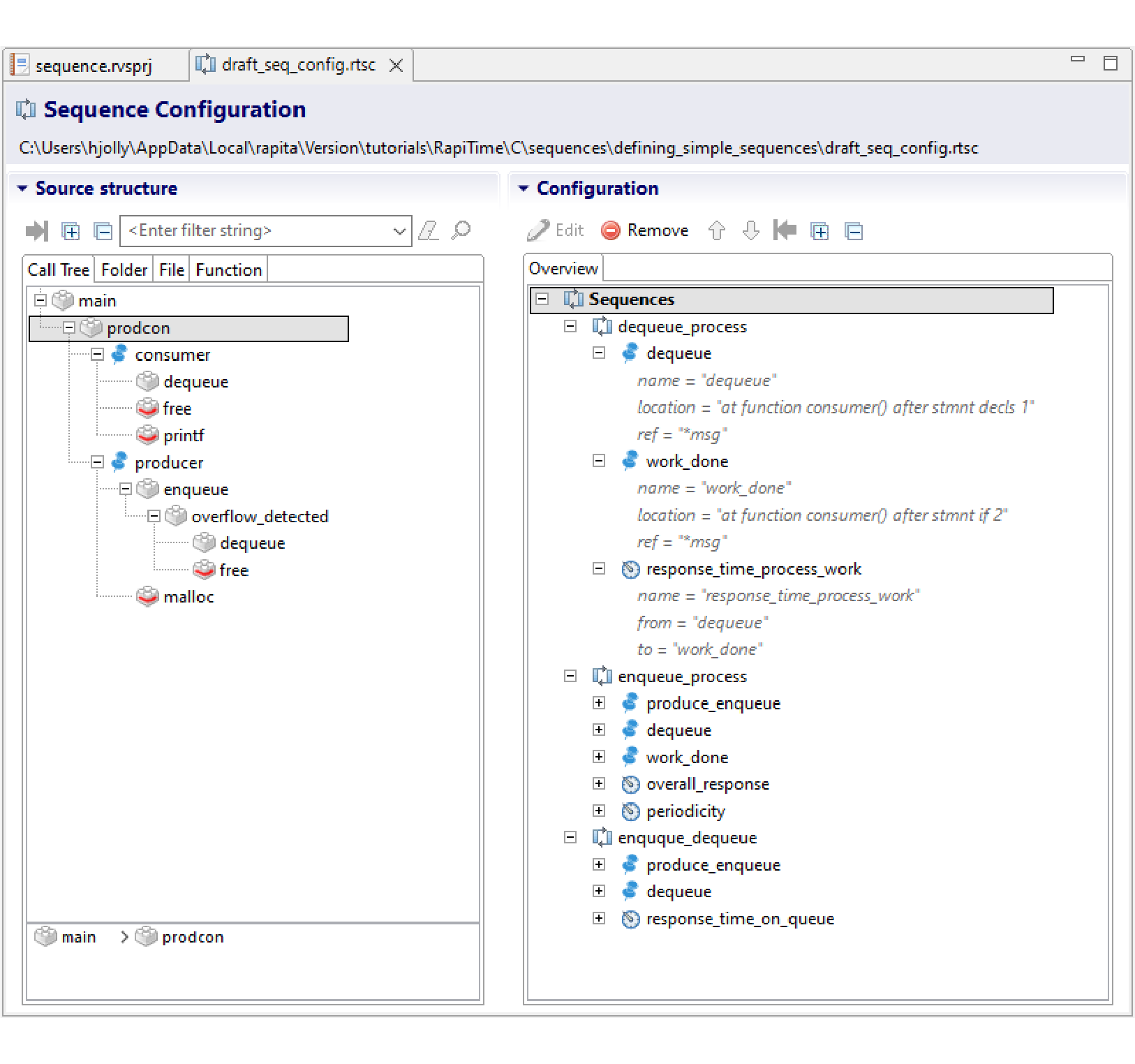

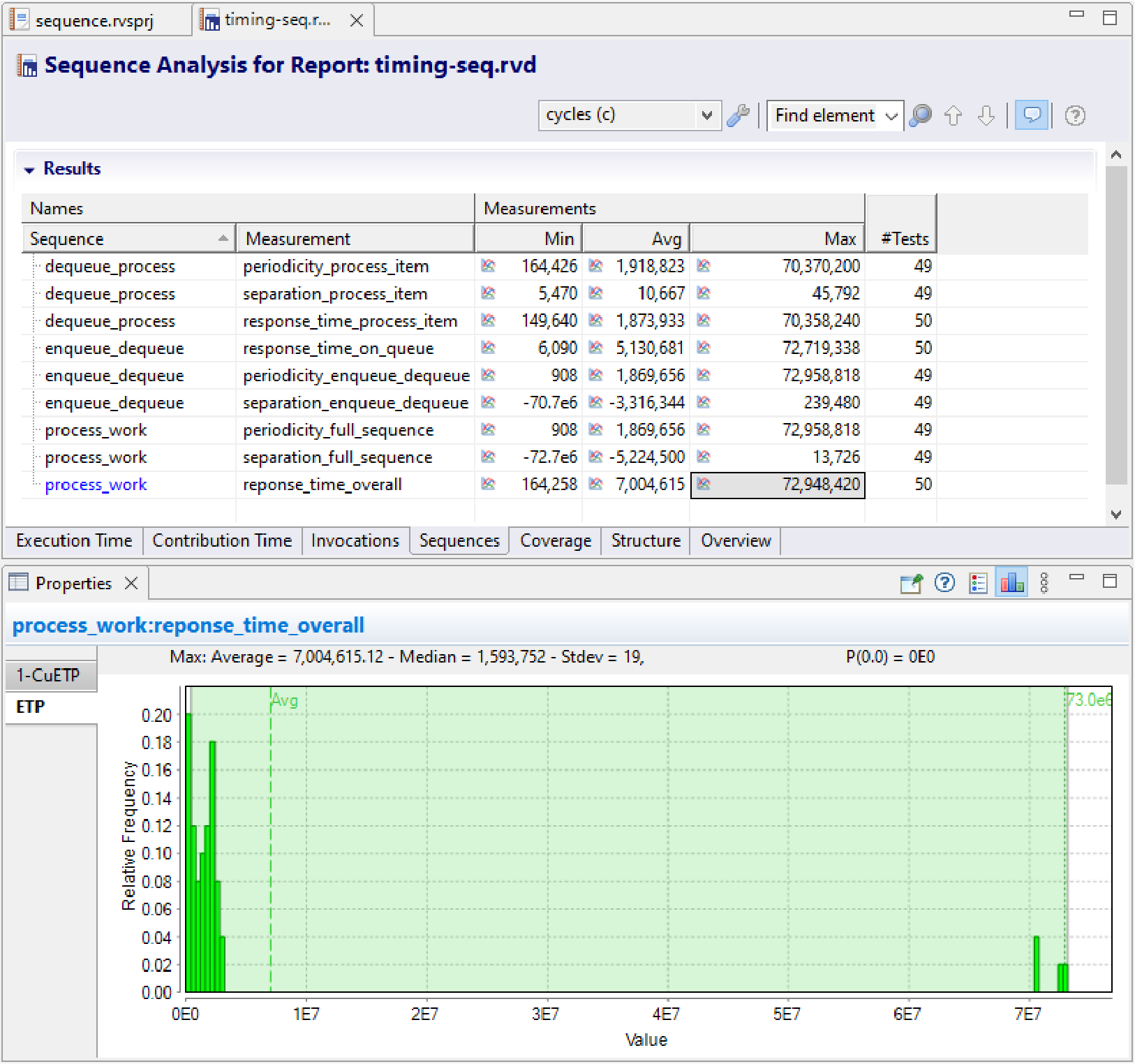

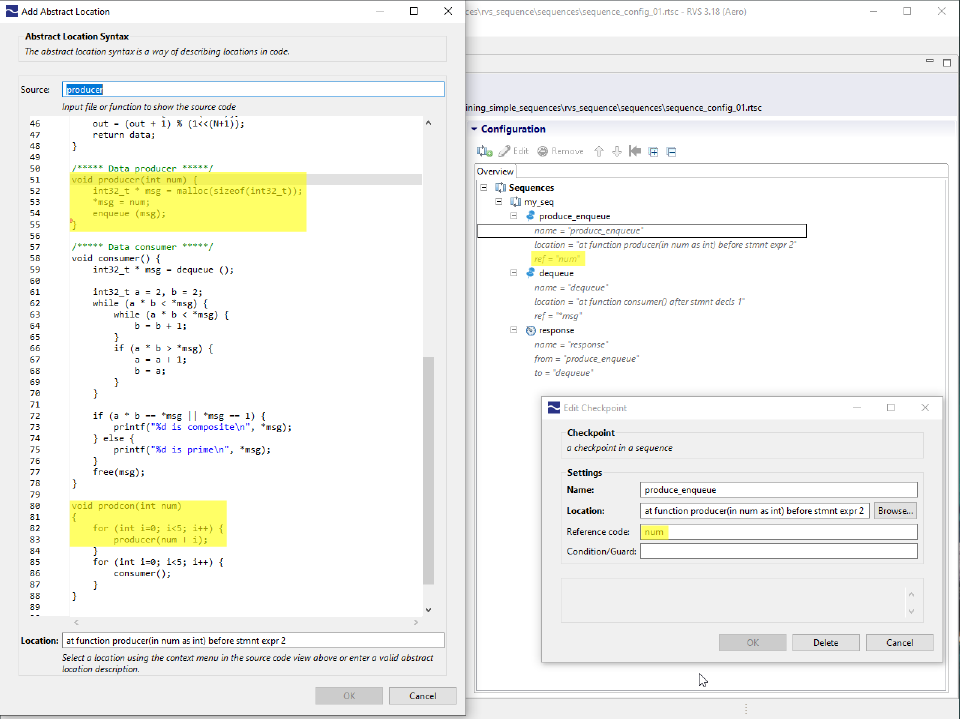

As of RVS 3.18, RapiTime includes a sequence analysis feature that provides a flexible framework for making these kinds of timing observations. This lets you define sequences of checkpoints within your code across which you want to take measurements. For each sequence, you can define the measurements you want taken, which can be the elapsed time between any two checkpoints within the sequence. After measurements have been defined, RapiTime can instrument your code appropriately, collect the necessary results during software execution, and display these results in your RapiTime report.

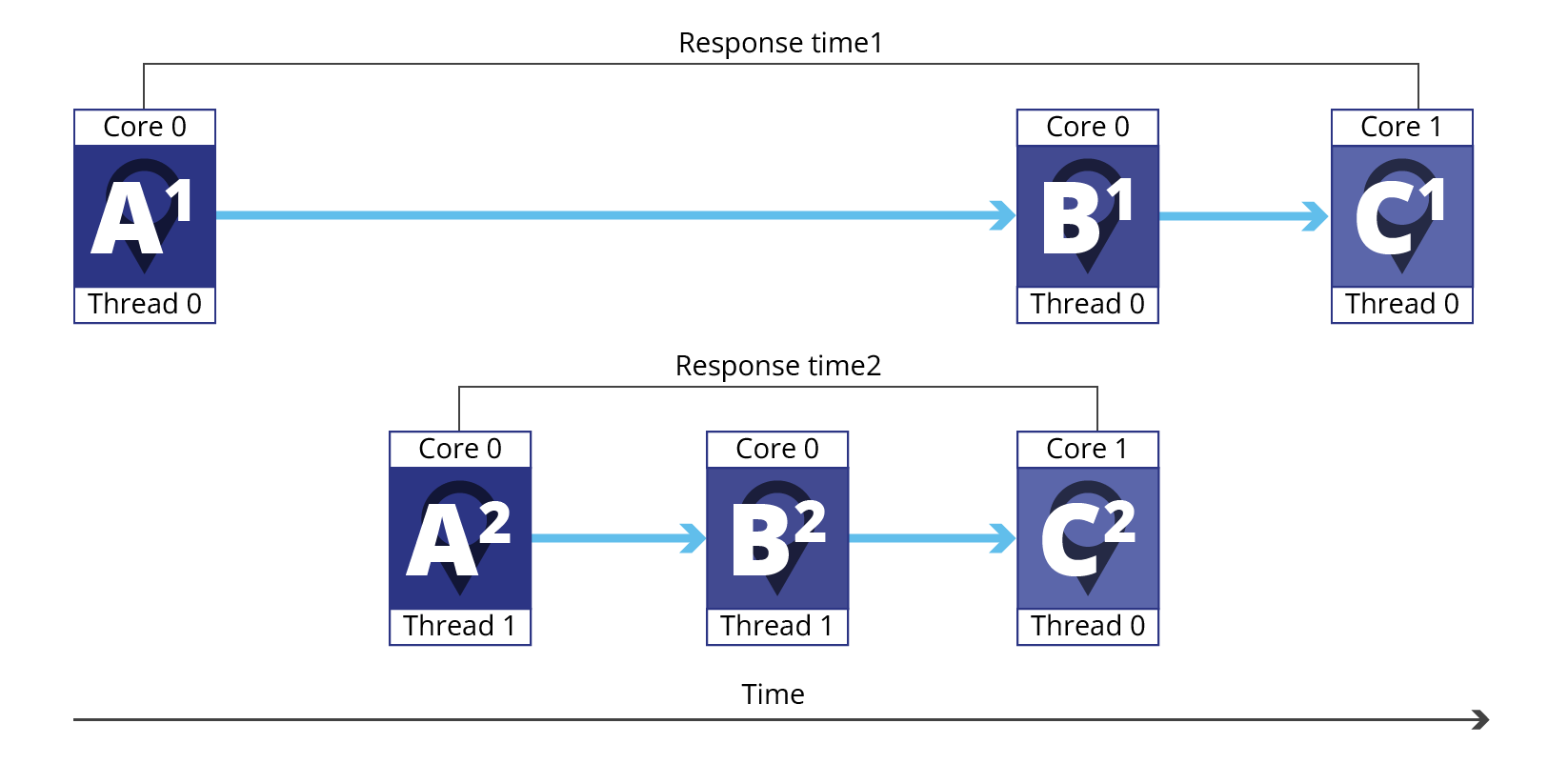

This flexible framework also supports multicore timing analysis such as that carried out in our MACH178 solution to meet A(M)C 20-193 objectives for multicore DO-178C projects. Sequence analysis makes it possible to measure end-to-end timing metrics for sequences of events when multiple tasks run simultaneously, even when sequences involve checkpoints executing on different cores (as shown below).

To support analysis in situations where multiple instances of a task may be running simultaneously, we needed to have a way to uniquely attribute checkpoints as belonging to a specific instance of a sequence. We did this by annotating each checkpoint with a sequence reference. When you define a checkpoint, you can supply a snippet of code that returns an integer shared by all checkpoints in the sequence, and is unique to each instantiation of the sequence. When each checkpoint is hit, this code is evaluated and the resulting integer is recorded in the checkpoint. This allows RVS to demultiplex sequences that execute simultaneously, so long as there is a distinguishing integer available.

We're looking forward to see how RVS’s new sequence analysis feature can help you verify your critical software. We’ll be building on the feature to support more complex, non-linear sequences and sequences where no single distinguishing integer reference is available in future RVS versions, stay tuned!

To learn more about sequence analysis, visit our feature page or contact us. For more information on multicore certification, visit our MACH178 page.

RVS 3.24 accelerates multicore software verification

RVS 3.24 accelerates multicore software verification

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Retro gaming with the Sim68020

Retro gaming with the Sim68020

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

Test what you fly - Real code, Real Conditions Webinar

Test what you fly - Real code, Real Conditions Webinar

Avionics Certification Q&A: CERT TALK

Avionics Certification Q&A: CERT TALK

XPONENTIAL 2026

XPONENTIAL 2026

DO-178C Multicore In-person Training (Heathrow)

DO-178C Multicore In-person Training (Heathrow)