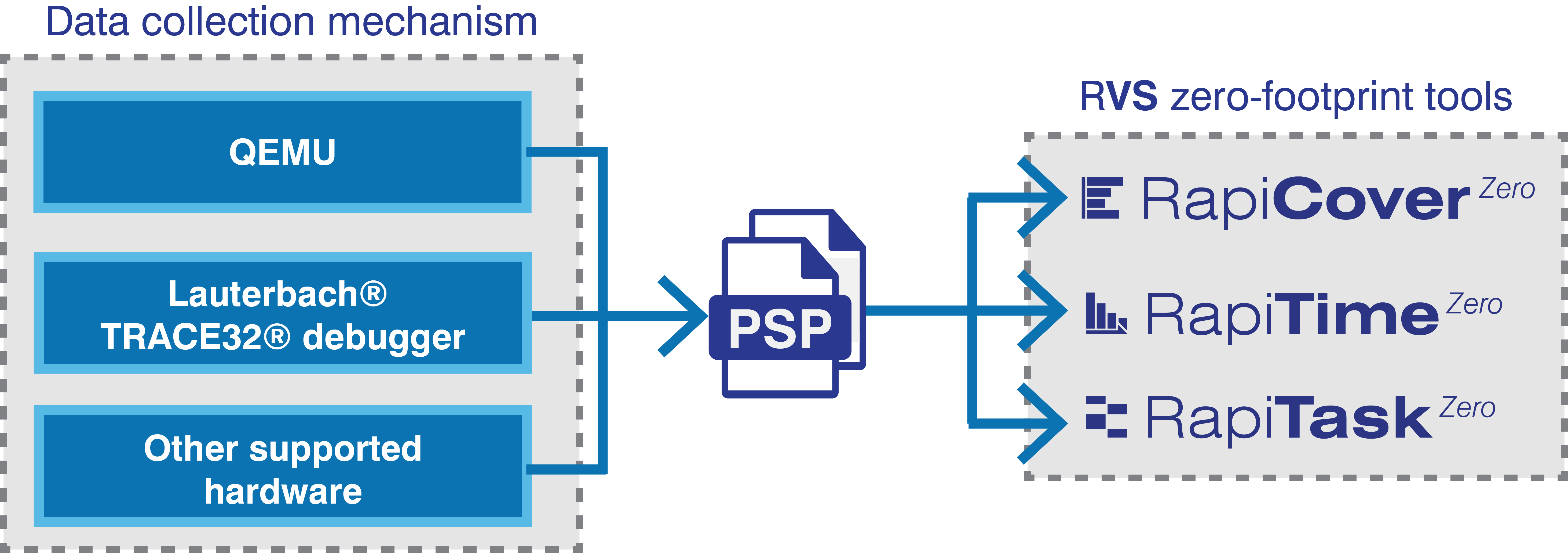

Zero-footprint RVS tools such as RapiCoverZero reconstruct information on the behavior of an application when it runs by using branch trace information captured from the platform the application is running on and combining this with information obtained from a disassembly of the application.

Software analysis by zero-footprint RVS tools has the following requirements:

- The platform (target and any external devices e.g. debuggers) must be capable of producing a branch trace without gaps to ensure that the full program trace can be reconstructed.

- The OS needs to make context switches observable. For some systems, supporting this may require modifications to be made to the OS.

- A Platform Support Package (PSP) is needed for RVS to interface with the development environment, including the target hardware and trace capture mechanisms, in order to convert the branch trace into a format that the RVS tool understands and disassemble the executable and parse the resulting object code.

PSPs are developed to be compatible with the following:

For a list of components that are already supported, see below. Note that we can add support for some components not listed below.

For detailed information on the requirements for zero-footprint tracing, see our Technical note.

For more information, contact info@rapitasystems.com.

Compilers

Platform Support Packages (PSPs) must be able to disassemble executables for further analysis. Typically, tools required for this are supplied as part of a toolchain unique to each compiler. The compilers PSPs already support are listed below:

- Arm Compiler

- CC-RH850

- Clang

- GCC

We can develop support for other compilers. For more information, contact us at info@rapitasystems.com.

Instruction sets

When code has been disassembled, Platform Support Packages (PSPs) must be able to understand the instruction set of the object code so they can parse it before it is used for subsequent analysis by zero-footprint RVS tools. The instruction sets PSPs already support are listed below:

- 68k

- AArch64

- ARM

- PowerPC

- RH850

- VISIUM

- x86

We can develop support for other instruction sets. For more information, contact us at info@rapitasystems.com.

Branch traces

For it to be possible to analyze executables generated by a platform by zero-footprint RVS tools, it must be possible to collect a branch trace from the platform*. Some targets generate branch traces by default, for example:

- Boards that have been developed to meet at least Class 2 of the Nexus message-based trace protocol

- ARM boards including an ARM ETM component

- Custom boards developed to produce branch traces

A debugger may be used to collect these branch traces from the target. Simulators may generate branch traces, or it may be possible to modify them to do so. Each Platform Support Package (PSP) is designed to support branch traces collected by a specific debugger or from a specific simulator. The debuggers and simulators PSPs already support are listed below:

|

Debuggers |

Simulators |

|---|---|

|

Lauterbach TRACE32 |

QEMU† |

|

PARTNER-Jet2 |

We can develop support for other debuggers and simulators. For more information, contact us at info@rapitasystems.com.

*In some cases, other approaches may be possible, such as using a branch map.

Real-time operating systems

For it to be possible to analyze executables generated by a platform by zero-footprint RVS tools, it must be possible to collect information on context switches made during software execution. Whether this is possible or not depends on the real-time operating system (RTOS) used and its configuration. Platform Support Packages must be able to understand context switch information to support further analysis of an executable by zero-footprint RVS tools. The RTOSs PSPs already support are listed below:

- eMCOS for AUTOSAR Adaptive Platform

- eMCOS for AUTOSAR Classic Platform (RV850)

- FreeRTOS

- SafeRTOS

- SYSGO PikeOS®

- Bare Metal (no OS)

We can develop support for other real-time operating systems. For more information, contact us at info@rapitasystems.com.

Feature applies to:

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Rapita partners with Asterios Technologies to deliver solutions in multicore certification

Rapita partners with Asterios Technologies to deliver solutions in multicore certification

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How emulation can reduce avionics verification costs: Sim68020

How emulation can reduce avionics verification costs: Sim68020

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

The EVTOL Show

The EVTOL Show

NXP's MultiCore for Avionics (MCFA) Conference

NXP's MultiCore for Avionics (MCFA) Conference

Embedded World 2026

Embedded World 2026

XPONENTIAL 2026

XPONENTIAL 2026