Rapita Systems S.L.

Multicore experts based in Barcelona

- Platform analysis

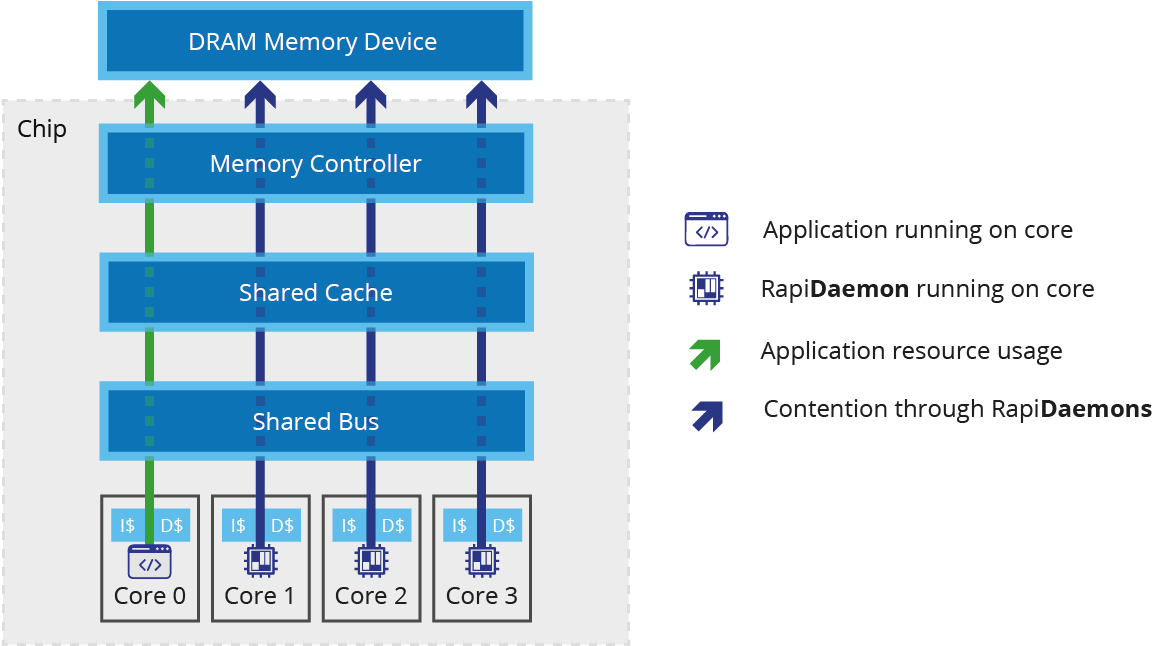

- RapiDaemon interference generators

About Rapita Systems S.L.

Rapita Systems S.L. (RSS) delivers solutions to verify and certify the software timing behavior of multicore processors in safety-critical embedded settings. This groundbreaking technology was pioneered at the BSC-CNS and is now mature and available commercially to industry via Rapita's MACH178 solution.

RSS was formed when Maspa Technologies S.L. was acquired by Danlaw Inc., Rapita Systems' parent company. Read more here.

Solutions

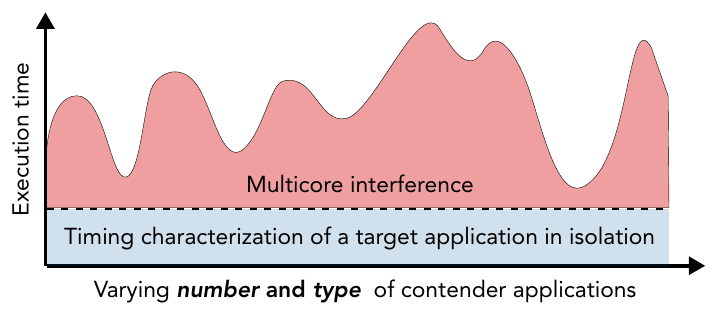

As Rapita Systems' Hardware Centre of Excellence, RSS provides a range of services and tools to support multicore verification, including platform analysis, RapiDaemon interference generators and contention modeling. These solutions are used to identify and measure the impact that interference can have on multicore-hosted software applications.

The solutions provides by RSS form a cornerstone of the MACH178 and Multicore Timing solutions, which provide a pathway to certifying the next generation of multicore embedded avionics and automotive systems.

Case study: Airbus

Rapita Systems S.L., then operating as Maspa Technologies S.L., played a key role in Airbus’ successful certification of the first ever ‘fully-automatic air-to-air refueling (A3R) operation with a boom system’. Timing analysis and characterization services were provided to Airbus that were key to building a certification argument for this advanced multicore avionics system.

Platform analysis

The verification of increasingly complex multicore COTS SoCs is a common challenge for embedded time-critical systems, which requires a detailed understanding of the hardware platform being used. Understanding a platform in enough depth to support verification, especially for projects undergoing DO-178C or similar certification, requires specialist knowledge.

The Rapita Systems S.L. team are world-leading specialists in understanding multicore platforms, with decades of experience in computer architecture and performance analysis.

This gives them the expertise needed to distil platform information from extensive (often 1,000s of pages long) technical reference manuals into actionable insights that support key activities including the following:

- Critical Configuration Settings (CCS) Analysis

- Interference Channel (IC) Analysis

- Hardware Event Monitor Analysis and Validation

RapiDaemons for analyzing timing interference

Qualifiable interference generators are at the heart of multicore timing analysis solutions. Rapita Systems S.L. (RSS) builds on long-term expertise in the design and deployment of specialized interference generators for timing analysis and identification of performance bottlenecks. Rapita Systems interference generators, developed by RSS, are sold as "RapiDaemons".

RapiDaemons are simple, well-crafted pieces of code that operate at the lowest interface between hardware and software. They are designed and refined to stress specific interference channels through applying contention on shared hardware resources.

Contention on shared hardware resources is a common source of interference in multicore platforms, as when a resource arbitrates multiple simultaneous requests, this can cause timing delays. RapiDaemons are designed to generate specific activities on specific shared resources, triggering a predefined effect on a specific interference channel with minimal impact on other interference channels. This supports the application of various verification methodologies for multicore systems.

Collins Aerospace and Rapita present award winning paper at DASC 2024

Collins Aerospace and Rapita present award winning paper at DASC 2024

Embedded Office GmbH & Co. KG and Rapita Systems announce strategic partnership

Embedded Office GmbH & Co. KG and Rapita Systems announce strategic partnership

Rapita Systems and LICRIT announce strategic partnership

Rapita Systems and LICRIT announce strategic partnership

Control Coupling Basics in DO-178C

Control Coupling Basics in DO-178C

Components in Data Coupling and Control Coupling

Components in Data Coupling and Control Coupling

The ‘A’ Team comes to the rescue of code coverage analysis

The ‘A’ Team comes to the rescue of code coverage analysis

Why there’s no standard approach for Data Coupling and Control Coupling Analysis

Why there’s no standard approach for Data Coupling and Control Coupling Analysis

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

ISO 26262

ISO 26262

Data Coupling & Control Coupling

Data Coupling & Control Coupling

Verifying additional code for DO-178C

Verifying additional code for DO-178C

HISC 2024

HISC 2024

DO-178C Multicore In-person Training (Munich)

DO-178C Multicore In-person Training (Munich)

DO-178C Multicore In-person Training (Fort Worth, TX)

DO-178C Multicore In-person Training (Fort Worth, TX)

DO-178C Multicore In-person Training (Toulouse)

DO-178C Multicore In-person Training (Toulouse)