SOI #2 - Development Review

After SOI #1, the next step is to develop your product. The first step in Development is to define the high-level requirements of your code. Later in Development, you will define low-level requirements. Developing high-level requirements involves refining the context of system requirements allocated to software and defining any software-specific requirements that do not map to system requirements as derived requirements. While defining both high and low-level requirements, you should ensure that you follow the processes you agreed to follow in your PSAC – your certification authority is likely to check that you have done so during future SOIs.

When your requirements are available, the next step is to design the architecture of your software and define its low-level requirements in order to define a system that can meet the high-level requirements you have identified. Design in DO-178C is the combination of architecture and low-level requirements. You will need to follow the design standards you said you would follow in your PSAC and provide evidence that you have done this.

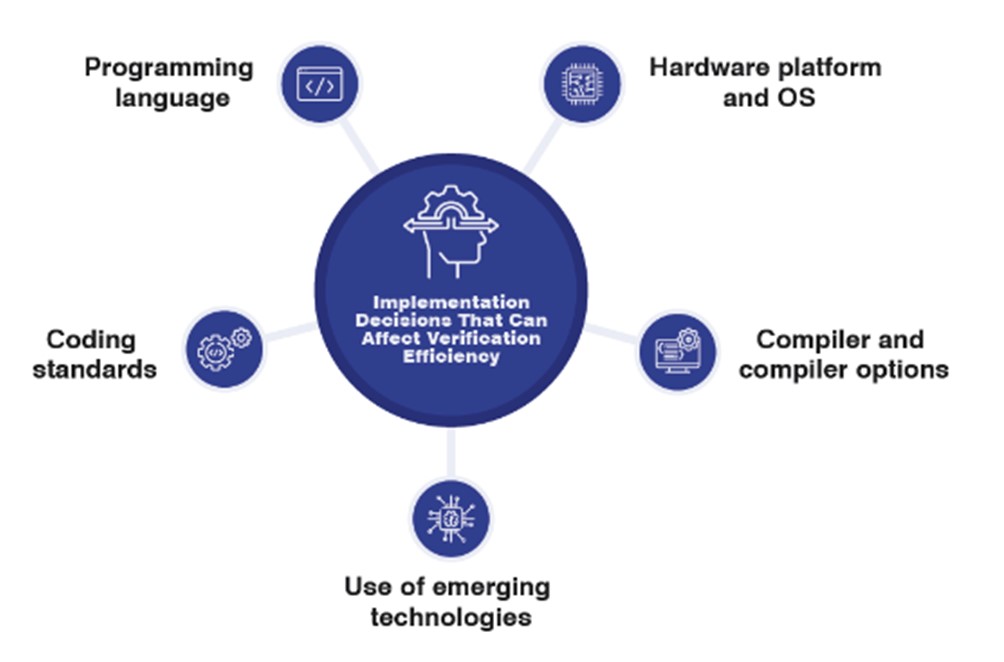

When your requirements and design are ready, the next step will be to implement your product in code. This is comparatively only a small part of the overall compliance process, usually taking 5% or less of overall effort. The decisions you make on how to implement your product can have major effects on your verification later on. These can make your verification much easier or much more difficult, and as a result cause your project to either run smoothly or incur delays. As verification takes much more effort than implementation, it’s worth considering the effects your decisions will have and making decisions that will reduce your verification effort.

Here are a few things you may want to consider:

- Choice of programming language(s)

- Choice of coding standard(s)

- Choice of hardware platform and operating system

- Choice of compiler and compiler options

- Use of emerging technologies (GPUs, multi-core processors etc.)

Before you have finished your Development, but when you have examples of each of your development artifacts (typically 60%-80% of your total expected artifacts), you should conduct SOI #2 with your certification authority. SOI #2 focuses on the development process and artifacts, but the review also considers verification processes that should be running concurrently with Development – specifically, the review activities being implemented. SOI #2 may also look forward to the verification phase to see if there are any examples where verification activities have provided feedback to development activities. This may include, for example, test case development or test environment development providing feedback to your requirements and design processes to ensure that test activities can completely verify the functionality expressed in your requirements and design.

Learn more about DO-178C by downloading the free 70-page handbook here.

RVS 3.24 accelerates multicore software verification

RVS 3.24 accelerates multicore software verification

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How emulation can reduce avionics verification costs: Sim68020

How emulation can reduce avionics verification costs: Sim68020

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

Embedded World 2026

Embedded World 2026

Test what you fly - Real code, Real Conditions Webinar

Test what you fly - Real code, Real Conditions Webinar

Avionics Certification Q&A: CERT TALK

Avionics Certification Q&A: CERT TALK