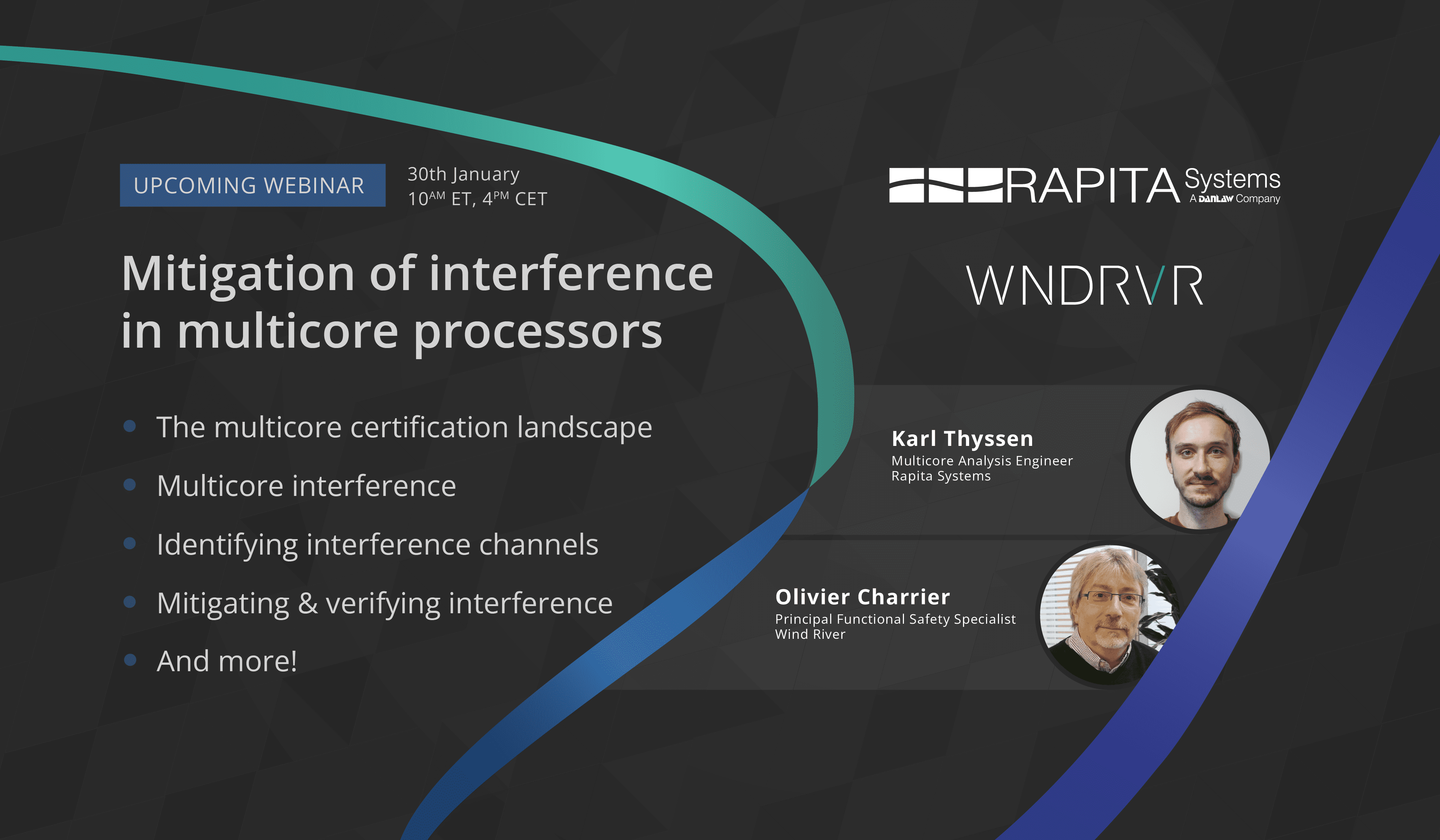

A technical webinar

Wind River™'s ARINC 653 compliant platforms help aerospace suppliers produce safety-critical avionics software for multicore architectures by using robust virtualization and partitioning technologies. These enable the partitioning of cores for different applications at different criticalities and also make it possible to run multiple applications on one specific core.

When incorporated into system-design considerations, these partitioning mechanisms enable developers to reduce the effects of interference on software performance. Interference can affect execution timing behavior (including WCET), as identified in the MCP_Software_1 objective of AC 20-193, AMC 20-193 and CAST-32A.

Rapita's Multicore Timing Solution provides the means for verifying that interference effects on the final hosted software are understood and bounded. By identifying and quantifying any interference in the system developed on the partitioned system, Rapita can help companies deliver an assessment of the robustness of the system, demonstrate it is free from interference and provide evidence of WCET to certification authorities.

- Examine partitioning mechanisms on Wind River's VxWorks® ARINC 653 RTOS.

- How to reduce interference between tasks on different cores.

- How Rapita demonstrates mitigation strategies are effective.

- How to quantify interference effects including timing behavior.

- Watch a practical demo on a T2080 multicore processor.

Rapita Systems and LICRIT announce strategic partnership

Rapita Systems and LICRIT announce strategic partnership

Rapita is proud to be an ISOLDE Partner

Rapita is proud to be an ISOLDE Partner

Components in Data Coupling and Control Coupling

Components in Data Coupling and Control Coupling

The ‘A’ Team comes to the rescue of code coverage analysis

The ‘A’ Team comes to the rescue of code coverage analysis

Why there’s no standard approach for Data Coupling and Control Coupling Analysis

Why there’s no standard approach for Data Coupling and Control Coupling Analysis

Introduction to Data Coupling and Control Coupling for DO-178C

Introduction to Data Coupling and Control Coupling for DO-178C

ISO 26262

ISO 26262

Data Coupling & Control Coupling

Data Coupling & Control Coupling

Verifying additional code for DO-178C

Verifying additional code for DO-178C

DO-178C Guidance: Introduction to RTCA DO-178 certification

DO-178C Guidance: Introduction to RTCA DO-178 certification

DASC 2024

DASC 2024

HISC 2024

HISC 2024

DO-178C Multicore In-person Training (Munich)

DO-178C Multicore In-person Training (Munich)

DO-178C Multicore In-person Training (Fort Worth, TX)

DO-178C Multicore In-person Training (Fort Worth, TX)