This post introduces a five step process for optimizations. The key to this process is to understand that step 4 (the technical work) is the most expensive, risky and time-consuming part. Therefore this process is designed to minimize the amount of time wasted in that step by avoiding optimizing the wrong things or spending unnecessary effort optimizing beyond the target.

- Identify Candidates

What are the optimization candidates? Make a shortlist of places to try optimizations and targets for what you would like to reduce there. Of course to do this, you need good information, as discussed in the previous post. - Analyse the potential gains and set targets for what you would like to be able to achieve.

If a candidate consumes 20% of the worst case execution time and you optimize it by 50%, you get at most 10% back. Is that enough justification to optimize it? - Know "what if".

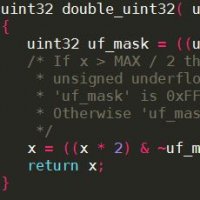

What if you were actually successful in optimizing the function by 50%? Does the worst case path switch somewhere else? If so, there's no point in continuing to optimize that function. - Try an optimization.

Actually do some technical work and perform an optimization. - Validate.

Measure the gain (or loss). Does the code still pass the tests? Did you achieve your target identified in step 2? Roll back if the work is not good enough.

Ian Dr Ian Broster is to run a half-day training session on software optimization at the forthcoming Reliable Software Technologies Conference - Ada Europe 2010.

The conference program is available here. Please register on-line and select Tutorial T5 (I. Broster).

The event takes place on the afternoon of Monday 14th June 2010 in Valencia, Spain.

For more information, or if you are unable to attend on this date and would like to take part in a similar tutorial, please feel free to contact us.

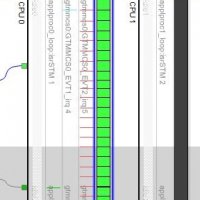

RVS 3.24 accelerates multicore software verification

RVS 3.24 accelerates multicore software verification

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Retro gaming with the Sim68020

Retro gaming with the Sim68020

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

Avionics and Testing Innovations

Avionics and Testing Innovations

Certification Together International Conference (CTIC)

Certification Together International Conference (CTIC)

HISC 2026

HISC 2026