This month sees the end of the three year FP7 parMERASA project – "Multi-core Execution of Parallelised Hard Real-Time Applications Supporting Analysability". The project has looked at the challenges of parallelized execution for mixed criticality in the domains of Avionics (Honeywell), Automotive (Denso) and construction machinery (Bauer), with academic partners from University of Augsburg, Barcelona Supercomputing Center, Université Paul Sabatier and Technical University of Dortmund.

In this blog I will summarize Rapita’s contributions to multicore verification from parMERASA, as presented at the public dissemination event in Barcelona last week. Our full slides can be found at http://www.parmerasa.eu/files/dissemination_event/verification.pdf

All Rapita’s developments are related to two of the big challenges for multicore embedded software and managing shared resources:

- Mutual exclusion of shared resources which is required for safety and security.

- Synchronisation between cores using barriers

Code Coverage for Multicore

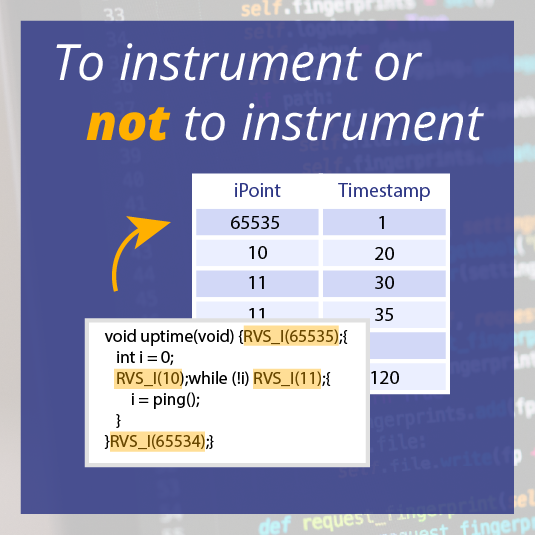

To support code coverage for multicore we have extended the coverage results visualization with support to show which core a particular statement of code was executed on. Also, we have full coverage reports for each core.

Most importantly, we have extended our RapiCover code coverage tool to assess coverage to and from barriers. This first means ensuring that all barriers in your software have been exercised during your requirements based testing. Further, this means you can ensure that every call made to a barrier has been covered by your test suite.

Further information on code coverage developments are in an earlier blog post: What are the implications of multicore devices on code coverage?

Visualization of Results

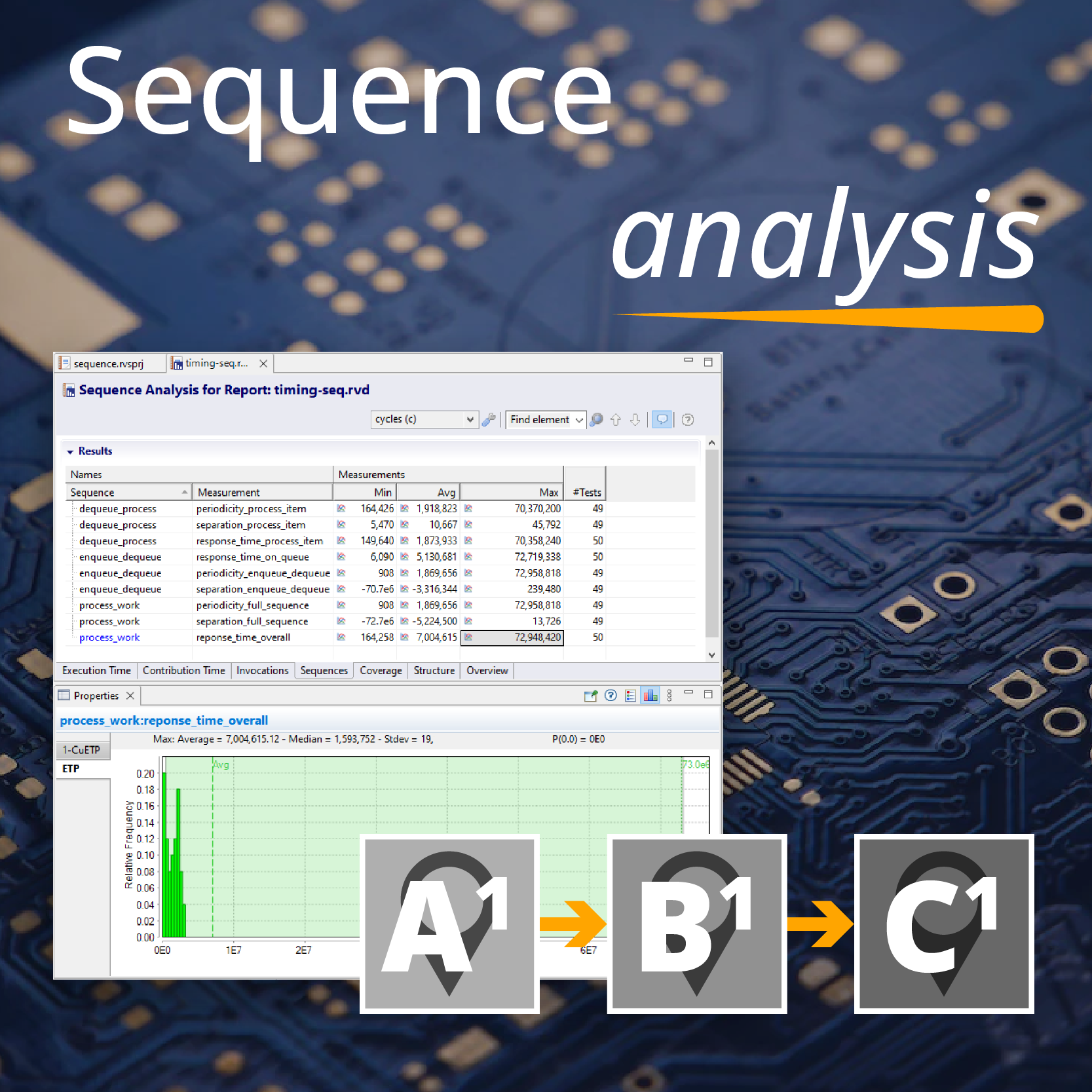

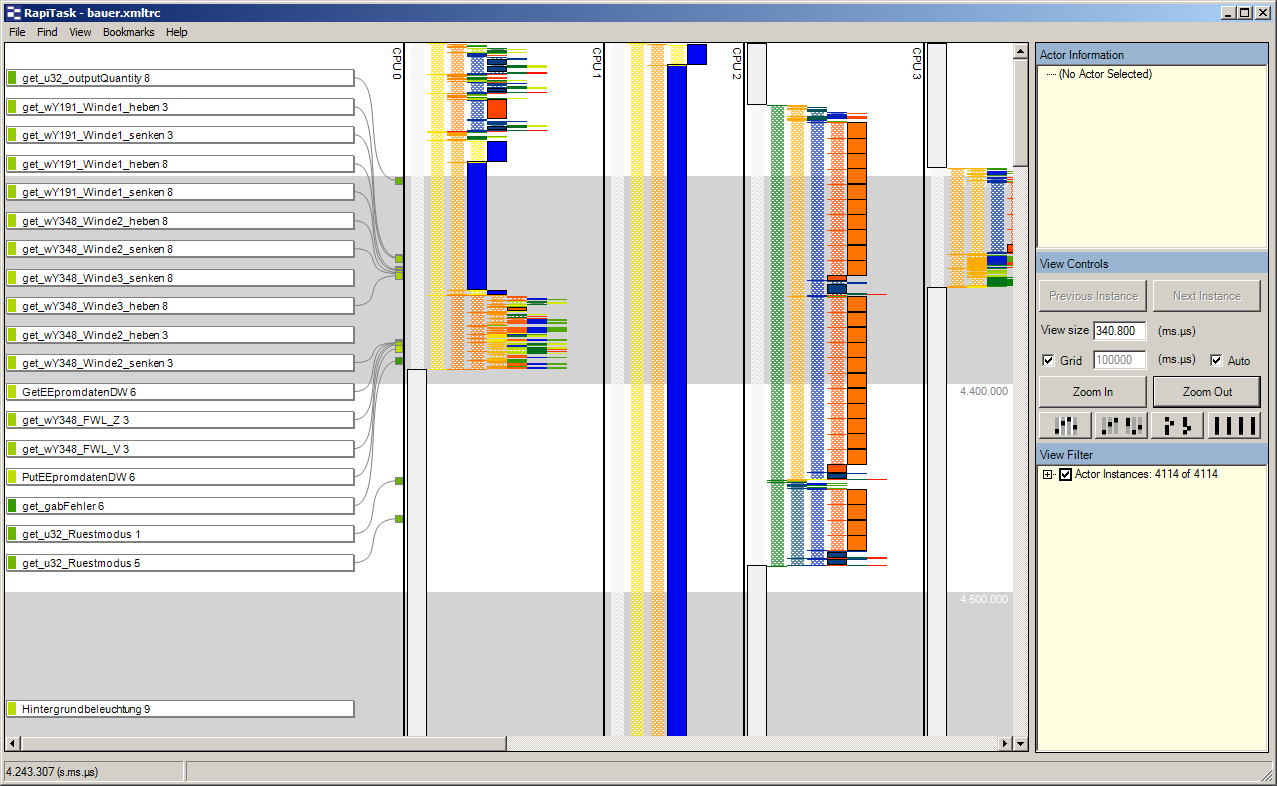

Visualization of task traces provides a simple mechanism to spot discrepancies in how a task is executing, such as multiple interrupts or priority inversion. Extending this to show multiple cores side by side, also means that synchronisation issues can be easily spotted. A large innovation from the project was development of the RapiTask tool (now part of RVS 3.2) to visualize traces on multiple cores, with data and task parallelization supported.

WCET for Multicore

One of the biggest challenges for multicore is measuring the worst case response time without returning overly pessimistic results. The pessimism is introduced when calculating lock waiting times during critical sections of code. The naïve assumption is that the worst case calculation for each thread needs to take into consideration the WCET from all the different threads that could also request that lock. What we found is that this level of pessimism can be reduced significantly if we only include the time spent in critical sections of the threads. We have developed extensions to RapiTime which take this into account, leading to tighter WCET results.

Data Dependencies

When parallelizing legacy software, it is important to identify data dependencies, such as global variables. During parMERASA we developed a tool to automatically find dependencies between code elements, based on global variable access. This is important to prevent read after write and write after read errors when the software is re-factored to multiple cores. The tool was used by the project partners to help during the parallelization process.

Further information

For more information on multicore verification support, please contact us.

For more information on the parMERASA projects, please visit the project website.

All the slides from the parMERASA dissemincation event are available on their website.

RVS 3.24 accelerates multicore software verification

RVS 3.24 accelerates multicore software verification

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Retro gaming with the Sim68020

Retro gaming with the Sim68020

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

Avionics Certification Q&A: CERT TALK

Avionics Certification Q&A: CERT TALK

XPONENTIAL 2026

XPONENTIAL 2026

DO-178C Multicore In-person Training (Heathrow)

DO-178C Multicore In-person Training (Heathrow)

Avionics and Testing Innovations

Avionics and Testing Innovations