Partitioning is well understood for single core systems. Two types of partitioning exist: space (or resource) partitioning, where partitioned components are isolated by operating on different hardware devices or different regions in a single device, and time partitioning, where partitioned components are isolated by operating in non-overlapping time periods (time slices). Both types of isolation are well understood for single core systems, and are implemented in many real-time operating systems used in the aerospace domain through the use of scheduling architectures such as ARINC 653.

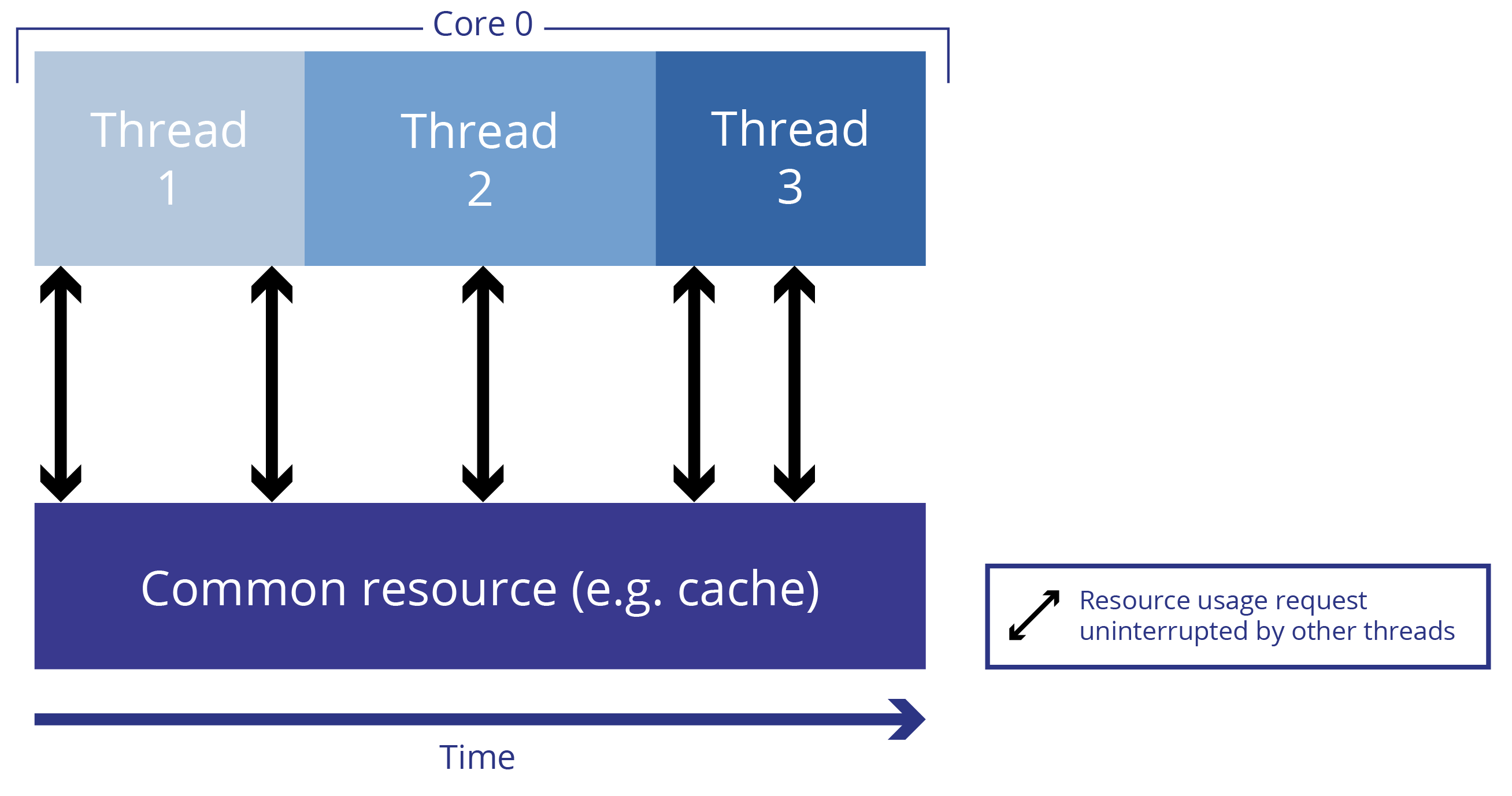

The most rigorous separation is termed robust partitioning. This is defined for single core systems in the ARINC 653 standard, where it refers to complete isolation of separated components, i.e. the execution of one component can have no effect on the other. To put this another way, the execution time of each thread is completely free from interference by the other threads (Figure 1).

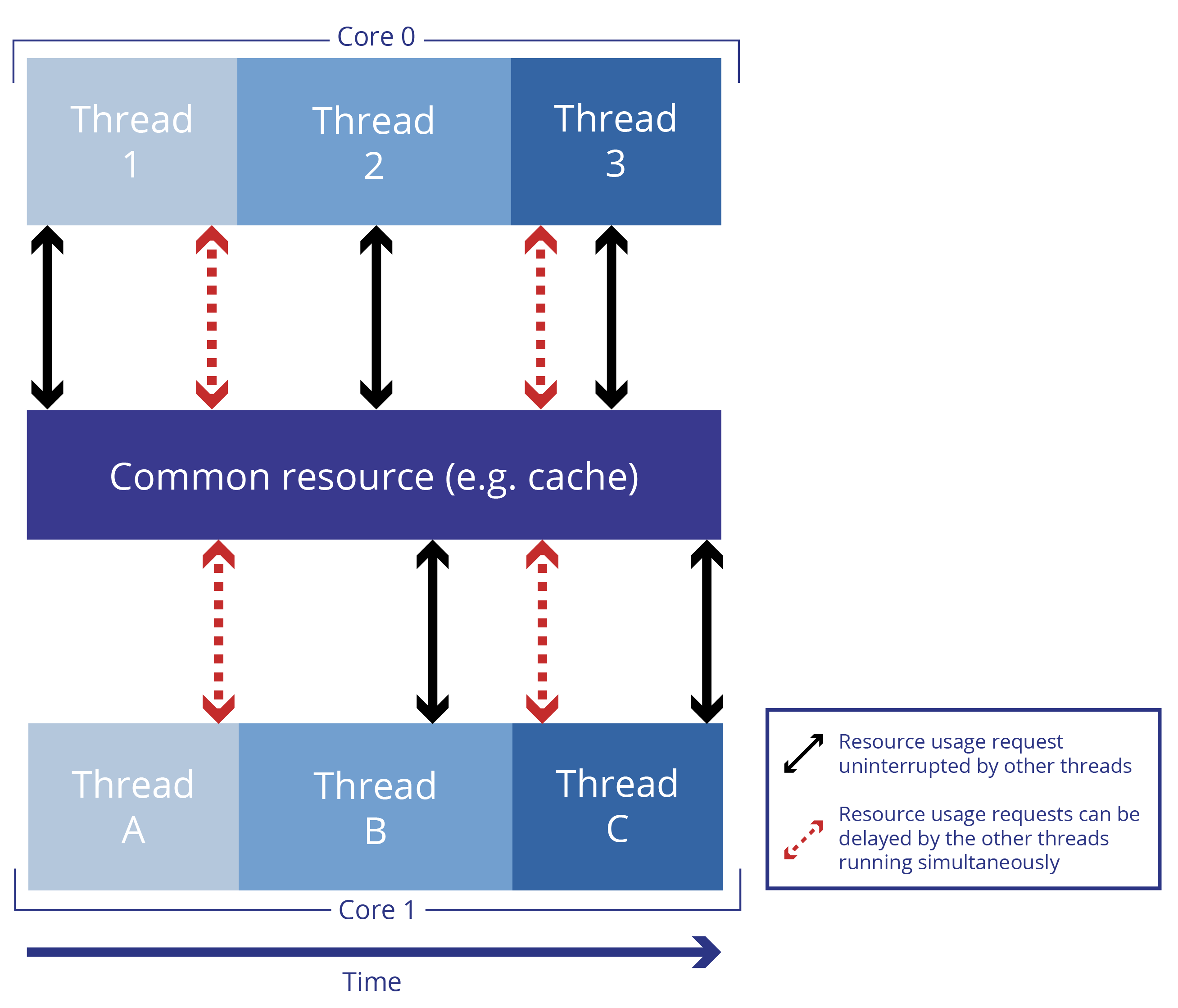

Most of the technology for partitioning of single core systems also applies to multicore systems. Multicore systems are more complex, however – for these systems, interference can exist between software hosted on different cores but running at the same time. Various interference channels can exist in such a system, such as for shared resources, and interference can increase software execution times and cause software to become non-deterministic (Figure 2). While the use of scheduling architectures such as ARINC 653 is enough to isolate partitioned software components in single core systems and ensure that the software is free from interference, this is not the case for multicore systems, where interference can be present even between (space) partitioned threads.

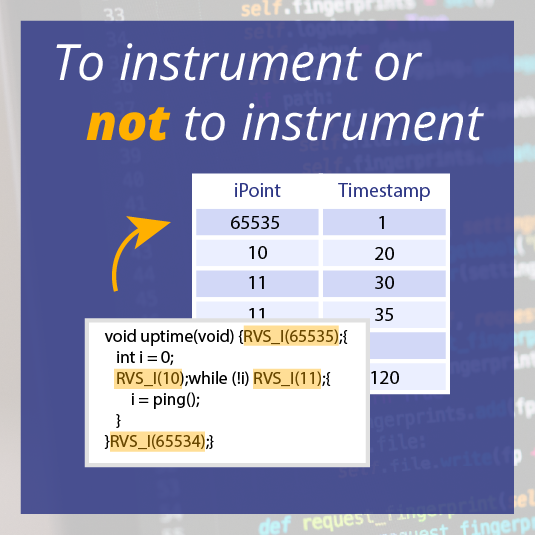

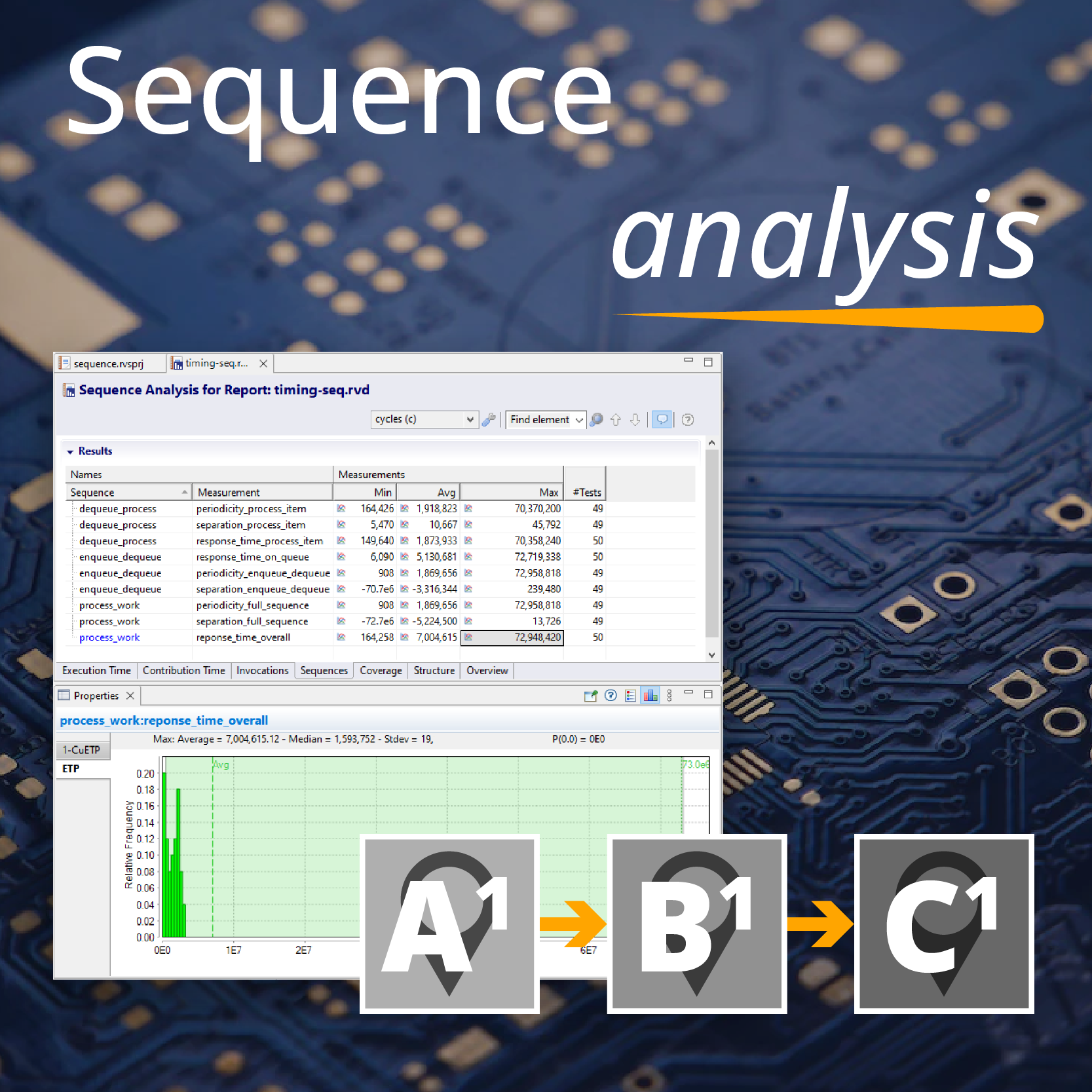

For multicore systems, robust partitioning according to its understood single core definition (isolation and freedom from interference) cannot be guaranteed by using a scheduling architecture alone. Because of this, we could infer that robust partitioning is not possible in multicore systems. CAST-32A, however, provides guidance on robust partitioning1, stating that robust space partitioning is comparable for single core and multicore systems, and providing a definition of robust time partitioning for multicore systems, stating that “[robust time partitioning is] achieved when, as a result of mitigating the time interference between partitions hosted on different cores, no software partition consumes more than its allocation of execution time on the core(s) on which it executes, irrespective of whether partitions are executing on none of the other active cores or on all of the other active cores.”. A sensible interpretation of this definition is that robust time partitioning is achieved when each software partition is guaranteed to meet its critical timing deadlines even when interference is present. To meet CAST-32A objectives and provide evidence that the software is robustly partitioned, the platform and hosted software must be tested by the analysis of software execution times when multicore interference is present. While various strategies may be used to mitigate against the actual interference present, this analysis is still necessary to demonstrate robust partitioning.

A major benefit of demonstrating robust partitioning is that it enables the use of software with different criticality levels to be executed on the same computing platform, provided that they are segregated into different partitions. Otherwise, even software that could nominally be certified to a lower Design Assurance Level would be forced to certify to the highest assurance level of any software on the system. Demonstrating robust partitioning also enables incremental assurance, allowing each supplier to test their software partitions independently of other suppliers. In this case, certification artifacts can be generated incrementally and aggregated by the system integrator. To be able to demonstrate robust partitioning to multicore systems and achieve these benefits, unique techniques are needed to support the analysis of software execution times when multicore interference is present, such as MACH178.

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Rapita partners with Asterios Technologies to deliver solutions in multicore certification

Rapita partners with Asterios Technologies to deliver solutions in multicore certification

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How emulation can reduce avionics verification costs: Sim68020

How emulation can reduce avionics verification costs: Sim68020

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

The EVTOL Show

The EVTOL Show

NXP's MultiCore for Avionics (MCFA) Conference

NXP's MultiCore for Avionics (MCFA) Conference

Embedded World 2026

Embedded World 2026

XPONENTIAL 2026

XPONENTIAL 2026