As it's the time of summer vacations, I thought it would be interesting to look at something a little more light-hearted than usual – a computer game designed to replicate the experience of low-level, bare metal programming on a hypothetical multicore system.

TIS-100 (www.zachtronics.com/tis-100) is a game that features a simulator of an imaginary, loosely-coupled, multicore system, together with a range of interesting programming problems.

The sixteen or so of the processor cores each provide two registers (only one of which is directly addressable), no memory, a very small program space (ten or so instructions), a set of input/output instructions and a collection of conditional jump instructions. Other types of cores also exist for stack-based memory or direct access memory.

It's fascinating and somewhat frustrating to have to work within the limitations of this architecture. Problems that would be trivial in other environments (for example, draw a histogram based on a sequence of numbers), suddenly become really difficult. A complicating factor is that it's virtually no space to include comments in the blocks of code, which makes reviewing or debugging code a real exercise in memory.

In addition to being a fun way of spending some time (assuming you find programming fun), this also seems like an excellent teaching tool for:

- Showing off some of the challenges of resource-limited programming that embedded developers are so familiar with.

- Exploring the difficulties of multi-core programming – putting deadlocks in my code seemed to happen too often.

Hopefully, games like these can also help to recruit a new generation of embedded programmers.

Another game that might be of interest is our own modified version of Tetris (Tetris Coverage Challenge) - after playing this, you can examine the code coverage you've achieved. Perhaps it doesn't teach programming directly, but it does give a pretty good demonstration of structural coverage analysis.

If you have any other suggestions for games that might be relevant to programmers, please feel free to leave them in the comments section, below.

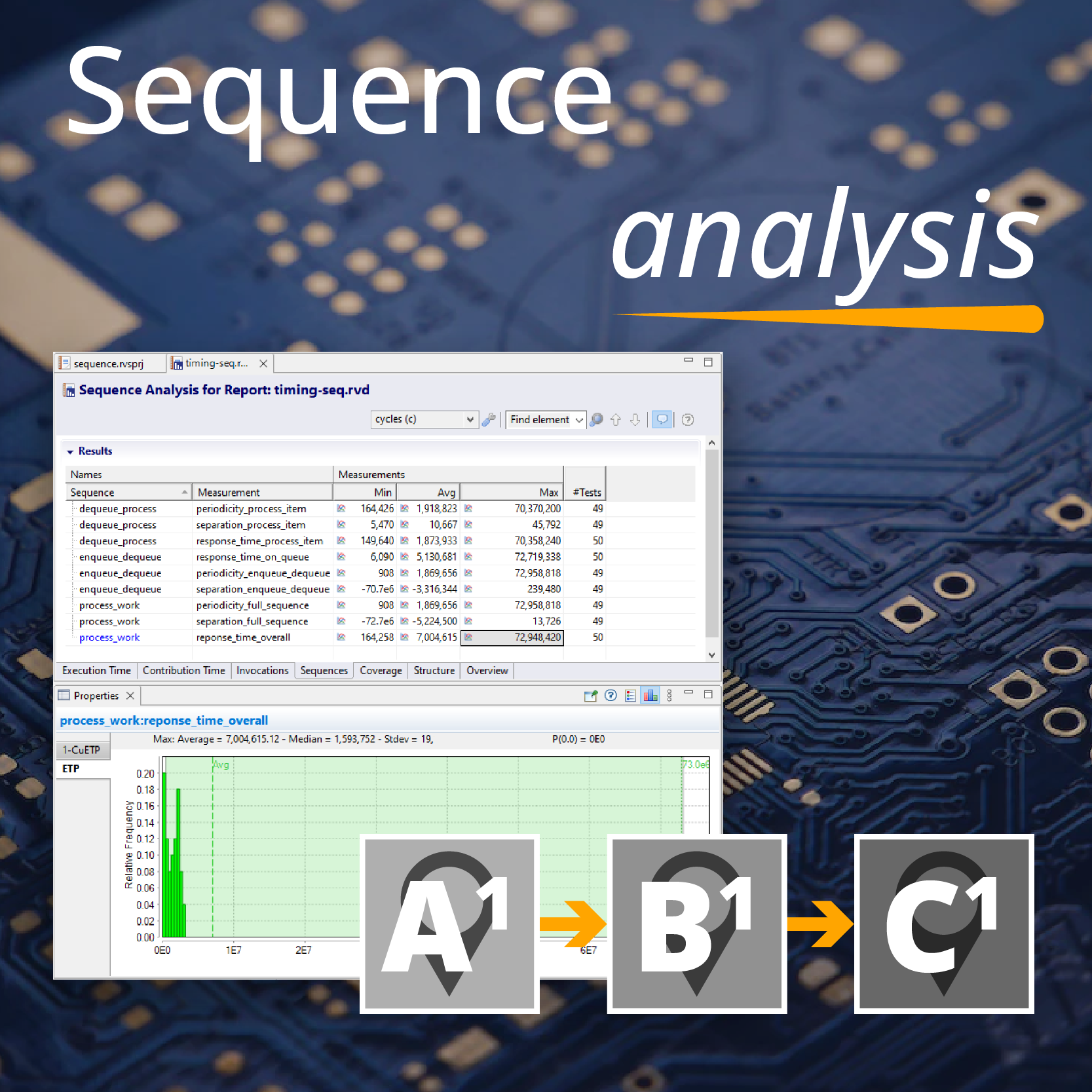

RVS 3.24 accelerates multicore software verification

RVS 3.24 accelerates multicore software verification

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Retro gaming with the Sim68020

Retro gaming with the Sim68020

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

Avionics Certification Q&A: CERT TALK

Avionics Certification Q&A: CERT TALK

XPONENTIAL 2026

XPONENTIAL 2026

DO-178C Multicore In-person Training (Heathrow)

DO-178C Multicore In-person Training (Heathrow)

Avionics and Testing Innovations

Avionics and Testing Innovations