Nested “case” labels are an obscure feature of C, and not often seen. However, examples do exist, typically hidden deep in standard library functions and our customers come across them from time to time. Here's a little article about how we recently brought support for them into RVS.

Nested “case” labels in practical C programs

For instance, the well-known sqlite3 library contains the following code:

switch( pOp->opcode ){

...

case OP_SorterNext: { /* jump */

VdbeCursor *pC;

int res;

pC = p->apCsr[pOp->p1];

...

res = 0;

...

goto next_tail;

case OP_PrevIfOpen: /* jump */

case OP_NextIfOpen: /* jump */

if( p->apCsr[pOp->p1]==0 ) break;

/* Fall through */

case OP_Prev: /* jump */

case OP_Next: /* jump */

...

pC = p->apCsr[pOp->p1];

res = pOp->p3;

This is found within the “sqlite3VdbeExec” function and forms the core of sqlite3's execution engine. Note that the local variables “pC” and “res” are shared between several different branches of the case; the label “case OP_PrevIfOpen:” is one of many that are nested within this block. Writing the code in this way made it possible to share these local variables between multiple “case” branches without needing to share them with the whole “sqlite3VdbeExec” function. Arguably, this makes the code clearer and easier to maintain.

Duff's Device

Duff's Device is a notorious example of a “switch” statement with nested case labels. It consists of a “switch” and a “do {} while” loop, in which the elements of the “switch” and loop are interleaved as follows:

int n = (count + 7) / 8;

switch (count % 8) {

case 0: do { *to = *from++;

case 7: *to = *from++;

case 6: *to = *from++;

case 5: *to = *from++;

case 4: *to = *from++;

case 3: *to = *from++;

case 2: *to = *from++;

case 1: *to = *from++;

} while (--n > 0);

}

In this example, “Duff's Device” copies memory, eight elements at a time. However, the total number of elements copied does not need to be divisible by eight. The first iteration can copy fewer than eight elements. This is arranged by entering the “do {} while” loop in the middle, via the nested “case” labels “case 7” through “case 1”. This avoids the need for a second group of copying statements, which would only be used when the number of elements to copy is not a multiple of eight.

“Duff's Device” is rarely used, though it frequently appears as an example of strange code that is nevertheless accepted by a C compiler. However, as the example of sqlite3 illustrates, Duff-like constructs do appear occasionally in practical C programs. Like the much-maligned “goto” statement, the nested “case” feature may be used with caution by C experts in order to write simpler or faster code.

Nested “case” labels and RVS

In version 3.5, RVS tools will gain support for “switch” constructs where “case” labels are nested. This means that Duff's Device (and constructs like it) are now supported. RapiTime timing analysis and RapiCover coverage analysis are both possible.

This is tricky to achieve because with nested switch/case, the program's control flow cannot easily be represented as a tree. The “switch” statement and the “do {} while” loop are interleaved: neither is inside of the other. Therefore, there is no straightforward way to represent the worst-case execution time of the “switch” statement. And for RapiCover, there is no easy way to determine which branches have been taken, because the entry points may be anywhere within the “switch”.

My solution to the problem was to reuse the existing support within RVS for “goto” statements. An early analysis pass searches each “switch” statement for nested “case” labels and treats them as “goto” labels. For each “case” label found in this way, a virtual “case” element is added as a child of the “switch” statement, containing a “goto” pointing at the appropriate label.

For example, if we had some code like this:

switch (x) {

case 1: if (y > 0) {

example_1 ();

case 2: example_2 (); break;

}

default: example_others (); break;

}

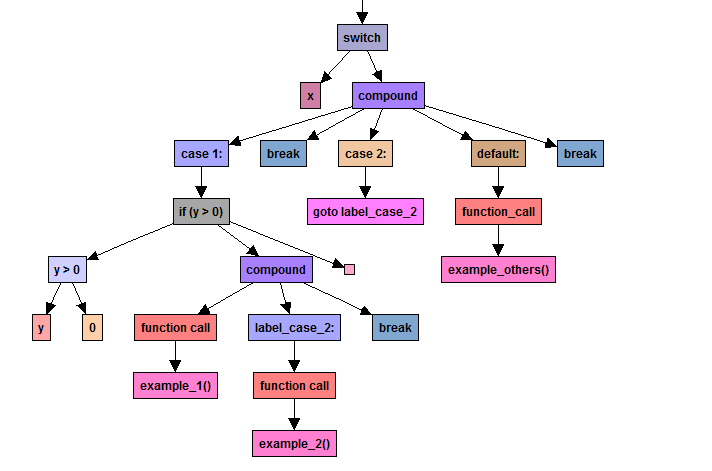

The source code is effectively represented internally using a syntax tree like this:

The modification means that all “case” labels have the same parent. For the purposes of all subsequent analysis stages, a “switch” with nested “case” labels is just like any other “switch”.

Conclusion

From time to time, there are situations where it is useful to nest “case” labels inside other blocks. Code may be simplified significantly by expert use of such techniques, much as expert use of “goto” can make code clearer. We work hard to support the way our customers work, and I'm pleased that RVS tools will now analyse this kind of construct.

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Rapita partners with Asterios Technologies to deliver solutions in multicore certification

Rapita partners with Asterios Technologies to deliver solutions in multicore certification

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How emulation can reduce avionics verification costs: Sim68020

How emulation can reduce avionics verification costs: Sim68020

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

The EVTOL Show

The EVTOL Show

NXP's MultiCore for Avionics (MCFA) Conference

NXP's MultiCore for Avionics (MCFA) Conference

Embedded World 2026

Embedded World 2026

XPONENTIAL 2026

XPONENTIAL 2026