Multicore processors are being used more and more in the development of critical embedded electronics, including avionics and automotive electronics. This is due to increasing demands on application functionality, the improved SWaP (size, weight and power) characteristics of these processors, and the increasing difficulty in sourcing single core processors.

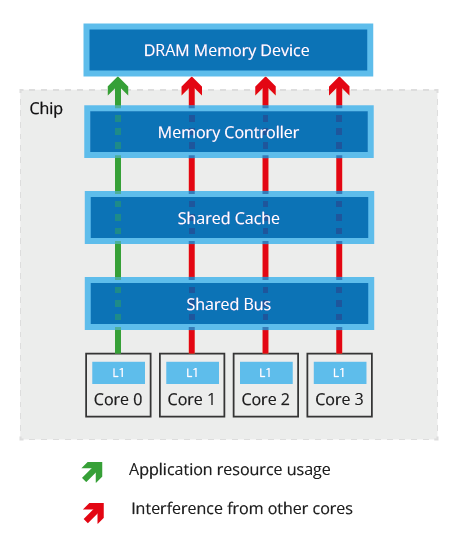

One of the main challenges in the adoption of multicore processors in critical electronics systems is that software running on one core can affect the execution of software running on another core. Multicore platforms are inherently non-deterministic with regards to their timing behavior, which poses a challenge for certification e.g. in accordance with DO-178C and AC 20-193, AMC 20-193 or CAST-32A guidance for aerospace software. Platform features that contribute to non-determinism are known as interference channels (Figure 1). These features can affect the ability of hosted software to meet its requirements. Some interference channels are obvious, but others are a little harder to identify. In this post, we discuss some of the better and less well-known sources of interference in multicore systems, using the NXP® T2080 processor as an example.

Types of interference

Interference channels can be classified in three categories: direct, indirect, and unknown.

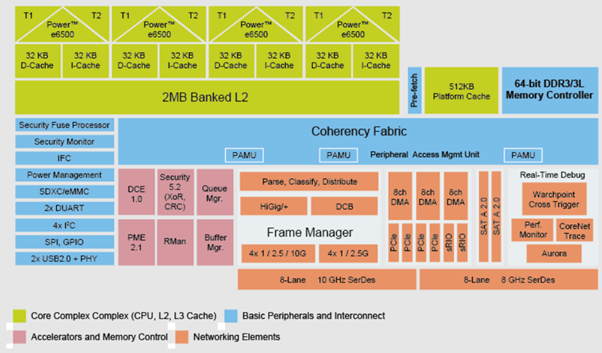

Examples of direct interference channels include shared on-chip resources such as shared caches, buses and memory management units, and off-chip resources such as I/O devices. Each shared resource may have multiple interference channels associated with it. The T2080 features an L2 cache that is shared across the four e6500 cores (Figure 2). Examples of direct interference channels relating to the L2 cache include one core causing the eviction of another core’s data from the cache, and the L2 cache having a limited bandwidth that is saturated by the four cores accessing the cache simultaneously.

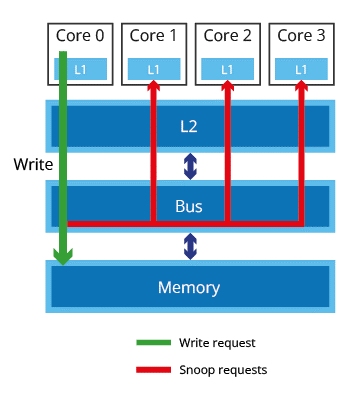

An example of an indirect interference channel on the T2080 is the potential slowdown induced by an excess of snoop requests on private caches due to cache coherency operations (Figure 3). Cache coherency is a mechanism by which shared data that gets loaded in private caches is updated to ensure that it is consistent with the data in main memory (depending on the configuration of the cache). Typically, when a core accesses shared data, the cache coherency mechanism will trigger snoop requests in order to detect any data in caches that needs to be invalidated.

Unknown interference channels are typically due to undocumented platform features. An example of these could be differences in the core’s performance and/or sensitivity to multicore interference due to the physical memory layout.

Identifying interference channels

The interference channels present in a platform depend on the chip and board architecture, the critical configuration settings of the system, which off-chip devices are being used, and how they are being used. For DO-178C certification in line with AC 20,193 or AMC 20-193 guidance, all the active interference channels in a multicore system must be identified and considered.

Identifying the potential interference channels in a specific system requires access to be available to comprehensive documentation describing multicore hardware from board and chip manufacturers and RTOS vendors, and the input of specialized engineers. The number of interference channels in a multicore system may be larger than you’d expect – having run a few projects involving the T2080, we’ve identified more than 150 potential interference channels on this system, depending on the configuration settings and peripherals used.

Learn more about interference

Do you need to identify the sources of interference on your system, or want to know more about sources of interference? Rapita’s MACH 178 solution and Multicore Timing Solution can help you.

RVS 3.24 accelerates multicore software verification

RVS 3.24 accelerates multicore software verification

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Retro gaming with the Sim68020

Retro gaming with the Sim68020

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

Test what you fly - Real code, Real Conditions Webinar

Test what you fly - Real code, Real Conditions Webinar

Avionics Certification Q&A: CERT TALK

Avionics Certification Q&A: CERT TALK

XPONENTIAL 2026

XPONENTIAL 2026

DO-178C Multicore In-person Training (Heathrow)

DO-178C Multicore In-person Training (Heathrow)