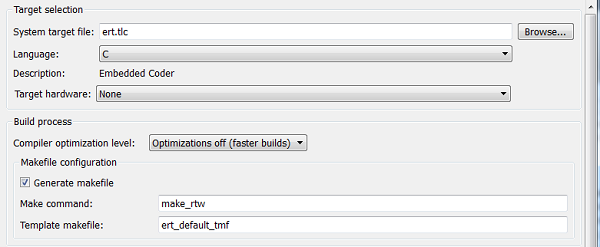

MATLAB® has a very flexible approach to building and configuring build systems. If you have set up your model to use the ert (embedded real-time target) simulation, you can check in the model configuration parameter windows and see:

Figure 1: Configuring makefiles

Ensure you tick Generate makefile. Copy the ert_lcc.tmf from: C:\Program Files\MATLAB\R2013b\rtw\c\ert

Switch into your build directory and build your model – you will see in the command window a line:

### Processing Template Makefile: C:\MATLAB\my_model\ert_lcc.tmf

And if you look in:

C:\MATLAB\my_model\my_model_ert_rtw

you will find the generated makefile:

C:\MATLAB\my_model\my_model_ert_rtw\my_model.mk

This has been generated by the

make_rtw

utility and is subsequently executed to create an executable.

You can now start modifying the build process. A full description of all the sections can be found in the Simulink® Coder->Customization->Target Development->Examples and How To section of the MATLAB documentation centre, but typical items are:

| OPTS | User specific compile options |

| USER_SRCS | Additional user sources, such as files needed by S-functions |

Other changes could be:

- Adding Folder Names to the Makefile Include Path;

- Adding Library Names to the Makefile.

Further down you can find the rules. You can add/modify these to include additional functionality as generating reports, checking version identities. For example, if you need a compiler/linker wrapper to provide additional build steps find the line:

include $(MATLAB_ROOT)\rtw\c\tools\lcctools.mak

Then you could insert something like:

ifeq ($(WRAPPER), 1) CC = C:\Wrapper\bin\lcc LD = C:\Wrappere\bin\lcclnk endif

At any time you can view the built makefile (.mk) to check that your rules are being generated correctly.

Many items above can be predefined and configured using System Target Files (STF) but the template makefiles (tmf) provides a rapid and convenient mechanism for setting up model builds.

MATLAB® and Simulink® are registered trademarks of The MathWorks, Inc. See mathworks.com/trademarks for a list of additional trademarks.

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

Hybrid electric pioneers, Ascendance, join Rapita Systems Trailblazer Partnership Program

Hybrid electric pioneers, Ascendance, join Rapita Systems Trailblazer Partnership Program

Magline joins Rapita Trailblazer Partnership Program to support DO-178 Certification

Magline joins Rapita Trailblazer Partnership Program to support DO-178 Certification

How to certify multicore processors - what is everyone asking?

How to certify multicore processors - what is everyone asking?

Data Coupling Basics in DO-178C

Data Coupling Basics in DO-178C

Control Coupling Basics in DO-178C

Control Coupling Basics in DO-178C

Components in Data Coupling and Control Coupling

Components in Data Coupling and Control Coupling

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

ISO 26262

ISO 26262

Data Coupling & Control Coupling

Data Coupling & Control Coupling

Verifying additional code for DO-178C

Verifying additional code for DO-178C

XPONENTIAL 2025

XPONENTIAL 2025

Avionics and Testing Innovations 2025

Avionics and Testing Innovations 2025

DASC 2025

DASC 2025

DO-178C Multicore In-person Training (Fort Worth, TX)

DO-178C Multicore In-person Training (Fort Worth, TX)