We recently tested a system with two different processors, a PowerPC and a TriCore. For anyone concerned with variability, the results make for interesting reading.

Last month Zoe explained how getting timing analysis into the development process early in a project can be useful for all sorts of reasons: [read more...].

This month I visited a customer where this was nicely illustrated. They have a system with two different processors, a PowerPC and a TriCore. Both will run the same software and there will be some crosschecking in a standard way for a safety critical application.

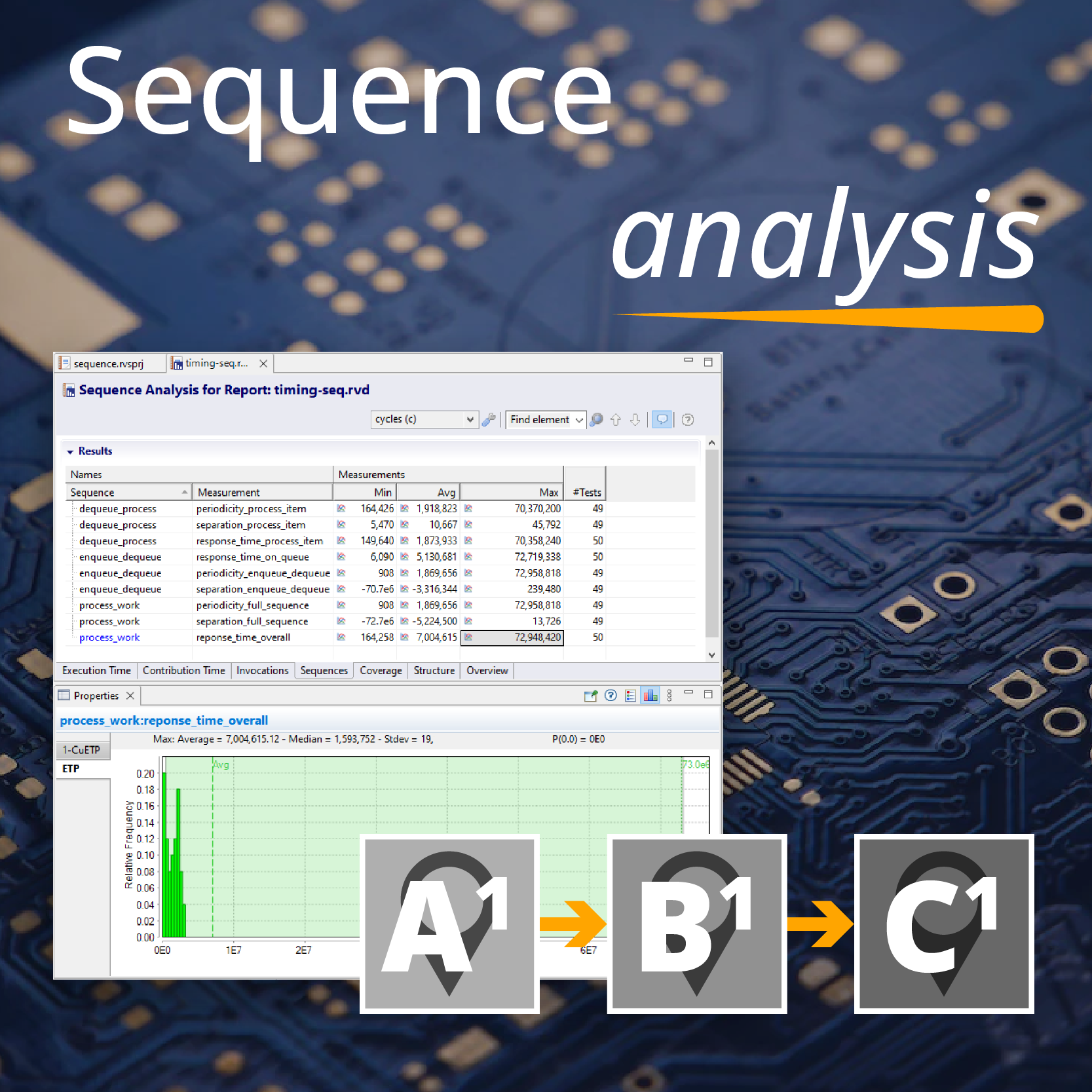

The customer added RapiTime to their development process well ahead of their delivery date, before the units of their system have been fully integrated. This is definitely recommended by us as good practice – finding potential timing problems early in development is going to make it cheaper to solve those problems than if issues are discovered when the deadline is approaching.

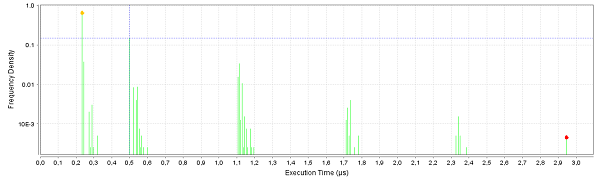

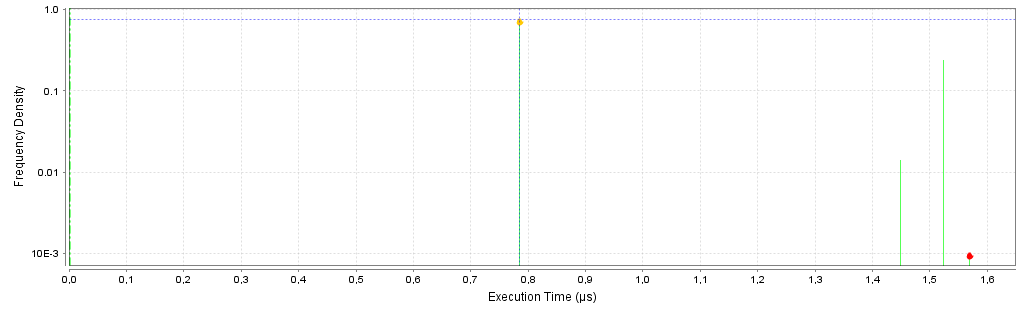

In testing one of the software units it was revealed that the PowerPC has a lot more variability in execution times than the TriCore. Looking at the graphs below (which are for a single function) you can see there is potentially another factor affecting the execution time of the PPC. Both graphs represent over 1000 executions of the function root. Finding this early means our customer has time to investigate the cause and find a solution.

It’s worth noting that although the TriCore was about half the average speed of the PPC (as measured by RapiTime) its worst case execution time was significantly better – because it doesn’t have this variability.

| Power PC | MPC5554 |

| TriCore | TC1796 |

| Compilers | Green Hills 5.2.4 (PPC) and Green Hills 5.1.3 (TriCore) |

[update]: Updated to clarify that the same function on Power PC and Tricore was executed the same number of times - which isn't immediately clear from the graphs.

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Rapita partners with Asterios Technologies to deliver solutions in multicore certification

Rapita partners with Asterios Technologies to deliver solutions in multicore certification

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How emulation can reduce avionics verification costs: Sim68020

How emulation can reduce avionics verification costs: Sim68020

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

Avionics Certification Q&A: CERT TALK (with Consunova and Visure)

Avionics Certification Q&A: CERT TALK (with Consunova and Visure)

DO-178C Multicore In-person Training (Heathrow)

DO-178C Multicore In-person Training (Heathrow)

Avionics and Testing Innovations

Avionics and Testing Innovations

Certification Together International Conference (CTIC)

Certification Together International Conference (CTIC)