Analyze interference in multicore systems

Analyze interference in multicore systems

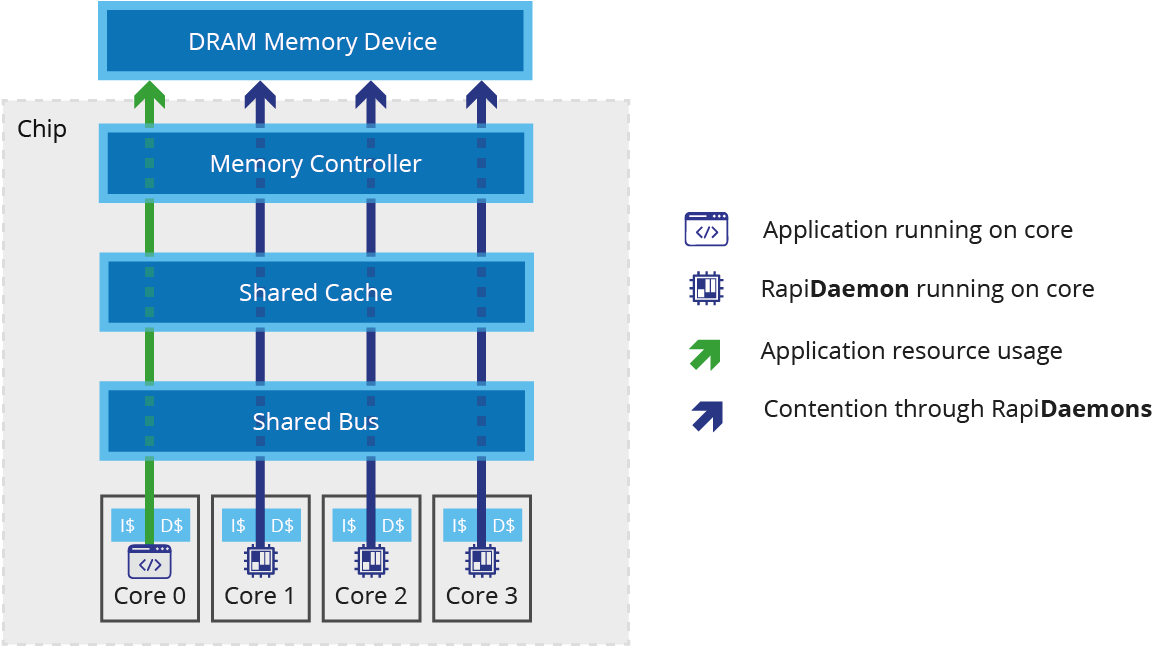

Interference effects in multicore systems can affect the timing behavior and predictability of software.

RapiDaemons support the analysis of interference in multicore systems by creating configurable degrees of contention on specific hardware resources during testing.

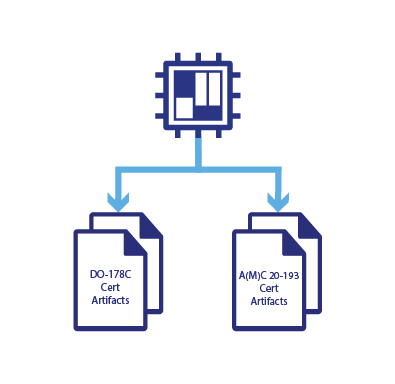

Produce evidence for DO-178C and A(M)C 20-193

DO-178C and A(M)C 20-193 together provide guidelines for the use of multicore systems in critical aerospace software development.

Some of the key objectives in A(M)C 20-193 relate to multicore timing analysis. RapiDaemons support this by applying configurable degrees of contention to hardware resources, allowing timing behavior to be analyzed while multicore interference is present in a controlled manner. The behavior of RapiDaemons is validated, making them suitable for use in DO-178C-compliant process.

Evaluate multicore hardware and RTOS

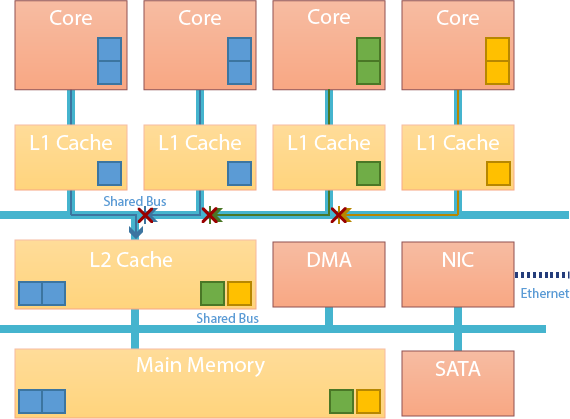

Different multicore systems can exhibit a range of interference behaviors. A combination of hardware, RTOS and software architecture decisions may support the development of software with predictable timing behavior, or may impede it.

RapiDaemons support the evaluation of multicore hardware and RTOSs by letting you quantify the timing behavior of applications running on these systems under a range of interference scenarios.

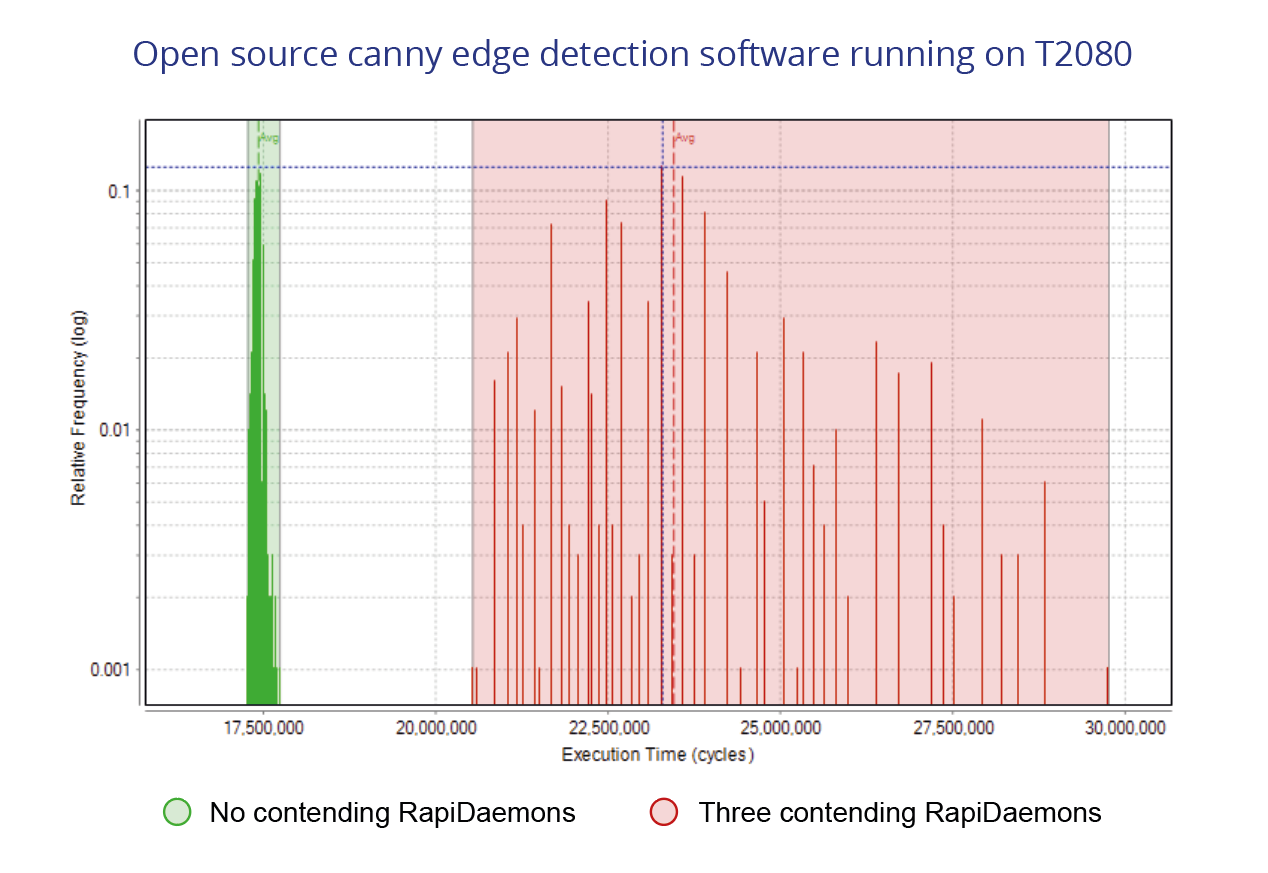

Evaluate worst-case timing scenarios robustly

RapiDaemons allow you to investigate a range of interference scenarios including “worst-case” scenarios and support robustness testing for timing behavior.

The Surrogate RapiDaemons tool produces Surrogate applications that produce a predefined interference behavior. This is often used to generate interference similar to that produced by a real application, letting you test realistic scenarios without needing to have every application running. To support robustness testing for timing behavior, the Discovery RapiDaemons tool lets you generate applications that cause extremely high interference.

Product features

-

Analyze interference in multicore systems Analyze multicore timing behavior under a range of interference scenarios.Discover this feature

Analyze interference in multicore systems Analyze multicore timing behavior under a range of interference scenarios.Discover this feature -

Verify hardware event monitors Verify the behavior of hardware event monitors on your system.Discover this feature

Verify hardware event monitors Verify the behavior of hardware event monitors on your system.Discover this feature -

Standard RapiDaemons Generate interference and study interference effects on common interference channels.Discover this feature

Standard RapiDaemons Generate interference and study interference effects on common interference channels.Discover this feature -

Advanced RapiDaemons Generate interference and study interference effects on complex interference channels.Discover this feature

Advanced RapiDaemons Generate interference and study interference effects on complex interference channels.Discover this feature -

Tuneable RapiDaemons Fine-grained analysis through configurable contention on shared resources.Discover this feature

Tuneable RapiDaemons Fine-grained analysis through configurable contention on shared resources.Discover this feature -

Surrogate RapiDaemon tool Automatically combine RapiDaemons to mimic the interference profile of your applications.Discover this feature

Surrogate RapiDaemon tool Automatically combine RapiDaemons to mimic the interference profile of your applications.Discover this feature -

Porting and customization RapiDaemons are customized for use with your multicore environment.Discover this feature

Porting and customization RapiDaemons are customized for use with your multicore environment.Discover this feature

Downloads

Frequently asked questions

-

What is a RapiDaemon?

A RapiDaemon is an application designed to create contention in a predictable and controlled manner on a specific shared resource in a multicore system. The effect of this contention can then be measured to identify interference channels and impacts on execution times.

Rapita have developed and optimized a set of standard RapiDaemons that target shared resources common to most multicore architectures, such as main memory. Some projects will require the creation of custom RapiDaemons for a specific architecture.

-

What are 'porting' and 'configuration' of RapiDaemons

Before timing analysis can begin, it is essential to confirm that existing RapiDaemons operate as intended on a specific board. If they do not, it may be necessary to customize them to make them behave as they are designed to (a similar intention to a target integration, where we get the instrumented application software running on a specific target).

'Porting’ and ‘configuration’ of RapiDaemons are roughly equivalent terms in this context. For RapiDaemons to work as intended, they need to go through a configuration phase where their internal parameters are tuned as required. They’re then tested to ensure compatibility with the platform in question.

Each type of RapiDaemon may be implemented for a different instruction-set architecture and platform. While the main logic behind their behavior remains the same, they must be ported to execute correctly on each new platform.

-

Do you verify the behavior of RapiDaemons?

Yes. We develop and test RapiDaemons against appropriate requirements, e.g. RapiDaemon M should access resource R when run N times.

-

Which hardware architectures can you analyze?

We can analyze almost all hardware architectures. Our engineers work with you to determine the optimal strategy for integrating our RVS tools with your target, including hardware characterization and design considerations to best fit the hardware you're using.

To work with an architecture that is new to us, we first identify which metrics we can collect from the hardware, then adapt RapiDaemons for the architecture and implement a strategy to collect data from it.

For a list of multicore architectures, RTOSs, boards and middleware we've worked with, see our compatibility page.

-

How do I use RapiDaemons?

RapiDaemons are delivered as object files that are compatible with your multicore platform. To configure these for use on your platform, these need to be linked together with your software’s object files. After this initial work, RapiDaemons can be automatically initialized using RapiTest and RapiTime.

When we deliver RapiDaemons, we include documentation describing how to configure and initialize them.

-

Do I need to use RVS tools to use RapiDaemons?

After linking RapiDaemons object files with your software (see “How do I use RapiDaemons?”), RapiDaemons are typically initialized through either RapiTest or RapiTime, which automate the initialization, making it easy to use RapiDaemons.

-

Do you have a standard set of RapiDaemons for my hardware?

Some of the multicore systems that we’ve worked with are listed in our FAQ “Which hardware architectures can you analyze?”. Standard RapiDaemons are available for many of the systems that we’ve analyzed. For more information, contact us.

-

What do I get when I get access to RapiDaemons?

We deliver RapiDaemons themselves as binary applications that are ported for compatibility with your multicore system. We also include documentation describing the purpose of each RapiDaemon in the library and how to use them.

We include support and maintenance for RapiDaemons, giving you access to our support team and to new RapiDaemons that we develop.

DO-330 Qualification kits are available for RapiDaemons to support the use of RapiDaemons in projects certifying to DO-178C or similar guidelines. These are available separately.

-

How are RapiDaemons licensed?

RapiDaemons are licensed as part of MACH178 or the Multicore Timing Solution. For more information, see those solutions or contact us.

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

SAIF Autonomy to use RVS to verify their groundbreaking AI platform

Hybrid electric pioneers, Ascendance, join Rapita Systems Trailblazer Partnership Program

Hybrid electric pioneers, Ascendance, join Rapita Systems Trailblazer Partnership Program

Magline joins Rapita Trailblazer Partnership Program to support DO-178 Certification

Magline joins Rapita Trailblazer Partnership Program to support DO-178 Certification

How to certify multicore processors - what is everyone asking?

How to certify multicore processors - what is everyone asking?

Data Coupling Basics in DO-178C

Data Coupling Basics in DO-178C

Control Coupling Basics in DO-178C

Control Coupling Basics in DO-178C

Components in Data Coupling and Control Coupling

Components in Data Coupling and Control Coupling

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

ISO 26262

ISO 26262

Data Coupling & Control Coupling

Data Coupling & Control Coupling

Verifying additional code for DO-178C

Verifying additional code for DO-178C

XPONENTIAL 2025

XPONENTIAL 2025

Avionics and Testing Innovations 2025

Avionics and Testing Innovations 2025

DASC 2025

DASC 2025

DO-178C Multicore In-person Training (Fort Worth, TX)

DO-178C Multicore In-person Training (Fort Worth, TX)