Misconception #1 Getting 100% MC/DC means you've got correct code

Congratulations! You’ve achieved 100% Modified Condition/Decision Coverage (MC/DC) during your testing. So does this mean that your code is correct? No!

Even though MC/DC considers the values taken on by Boolean variables, it has no concept of the "right" or "wrong" outcome from your code. To do this, it would need to compare the values of the Boolean variables to what the requirements say. Doing this is actually the job of the functional tests - MC/DC measurement simply reports on how well the functional tests demonstrate that the implementation meets the requirements. In other words, MC/DC is all about the effectiveness of the test, not the results.

You can easily have correct code that is not well-tested, and hence not achieve 100% MC/DC. Equally, you can achieve 100% MC/DC without having correct code.

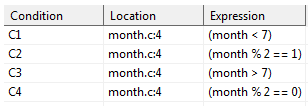

For example, consider this expression for determining whether the month variable represents a 31-day month:

if (((month < 7) && (month % 2 == 1)) || ((month > 7)

&& (month % 2 == 0)) {

...

}

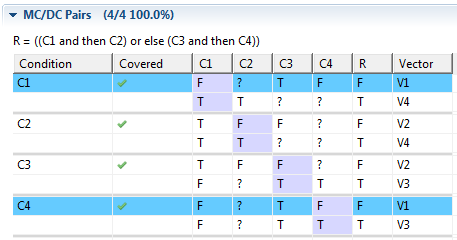

We can achieve 100% MC/DC with the following test vectors:

V1 month = 9

V2 month = 2

V3 month = 8

V4 month = 1

[Footnote: because the variable “month” is used in each condition, we’ve used Masking MC/DC here – where, for example, a false value for C1 “masks” the value of C2 – if C1 is false, it doesn’t matter what the value of C2 is, as that subexpression can never be true.]

What has not been exposed by these tests is what happens when month=7 – the code doesn’t recognize this as a 31-day month.

The misconception that getting 100% MC/DC means you've got correct code is wrong because our example achieves 100% MC/DC and it contains a fault which isn't exposed by the testing.

RVS 3.24 accelerates multicore software verification

RVS 3.24 accelerates multicore software verification

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita Systems and Avionyx Announce Strategic Partnership to Offer Best-in-class Avionics Solutions

Rapita System Announces New Distribution Partnership with COONTEC

Rapita System Announces New Distribution Partnership with COONTEC

Retro gaming with the Sim68020

Retro gaming with the Sim68020

RVS gets a new timing analysis engine

RVS gets a new timing analysis engine

How to measure stack usage through stack painting with RapiTest

How to measure stack usage through stack painting with RapiTest

What does AMACC Rev B mean for multicore certification?

What does AMACC Rev B mean for multicore certification?

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve multicore DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

How to achieve DO-178C certification with Rapita Systems

Certifying Unmanned Aircraft Systems

Certifying Unmanned Aircraft Systems

DO-278A Guidance: Introduction to RTCA DO-278 approval

DO-278A Guidance: Introduction to RTCA DO-278 approval

XPONENTIAL 2026

XPONENTIAL 2026

DO-178C Multicore In-person Training (Heathrow)

DO-178C Multicore In-person Training (Heathrow)

Avionics and Testing Innovations

Avionics and Testing Innovations

Certification Together International Conference (CTIC)

Certification Together International Conference (CTIC)